Практическое занятие № 34-35

Тема: «Проектирование статического D-триггера и D-триггера, работающие по фронту»

Цель: овладение навыками логического проектирования триггерных схем в различных функциональных базисах.

Теория

Статические D-триггеры

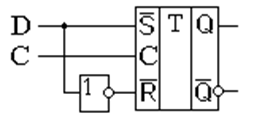

В RS-триггерах для записи логического нуля и логической единицы требуются разные входы, что не всегда удобно. При записи и хранении данных один бит может принимать значение, как нуля, так и единицы. Для его передачи достаточно одного провода. Как мы уже видели ранее, сигналы установки и сброса триггера не могут появляться одновременно, поэтому можно объединить эти входы при помощи инвертора, как показано на рисунке 1.

Рисунок 1 - Принципиальная схема

D триггера (защелки)

Такой триггер получил название D триггер. Название происходит от английского слова delay — задержка. Конкретное значение задержки определяется частотой следования импульсов синхронизации.

Таблица истинности D триггера достаточно проста, она приведена в таблице 1. Как видно из этой таблицы, данный триггер способен запоминать двоичный сигнал по синхросигналу и хранить один бит двоичной информации.

Таблица 1. Таблица истинности D триггера

|

С |

D |

Q(t) |

Q(t+1) |

Пояснения |

|

0 |

x |

0 |

0 |

Режим хранения информации |

|

0 |

x |

1 |

1 |

|

|

1 |

0 |

x |

0 |

Режим записи информации |

|

1 |

1 |

x |

1 |

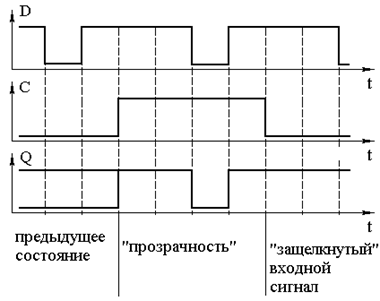

Во всех рассмотренных ранее схемах синхронных триггеров синхросигнал работает по уровню, поэтому триггеры называются триггерами, работающими по уровню, или статическими триггерами. Ещё одно название таких триггеров, пришедшее из иностранной литературы — триггеры-защёлки. Легче всего объяснить происхождение этого названия по временной диаграмме сигналов, приведенной на рисунке 2.

Рисунок 2 - Временная диаграмма сигналов работы D триггера

По этой временной диаграмме видно, что триггер-защелка хранит данные на выходе только при нулевом уровне на входе синхронизации. Если же на вход синхронизации подать активный высокий уровень, то напряжение на выходе триггера будет повторять напряжение, подаваемое на его вход.

Входное напряжение запоминается только в момент изменения уровня напряжения на входе синхронизации C с высокого уровня на низкий уровень. Входные данные как бы «защелкиваются» в этот момент, отсюда и название — триггер-защелка.

D триггеры, работающие по фронту (динамические триггеры)

Фронт сигнала синхронизации, в отличие от высокого (или низкого) потенциала, не может длиться продолжительное время. В идеале длительность фронта равна нулю. Поэтому в триггере, запоминающем входную информацию по фронту, не нужно предъявлять требования к длительности тактового сигнала.

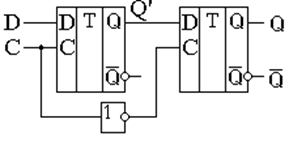

Триггер, запоминающий входную информацию по фронту, может быть построен из двух триггеров, работающих по потенциалу. Сигнал синхронизации будем подавать на эти триггеры в противофазе. Схема такого триггера приведена на рисунке 3.

Рисунок 3 - Схема D-триггера, работающего

по фронту

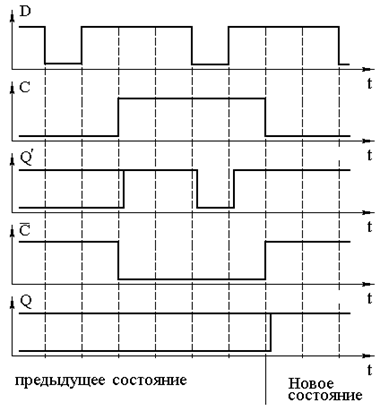

Рассмотрим работу схемы динамического триггера, приведенной на рисунке 3 подробнее. Для этого воспользуемся временными диаграммами, показанными на рисунке 4. На этих временных диаграммах обозначение Q΄ соответствует сигналу на выходе первого триггера. Так как на вход синхронизации второго триггера тактовый сигнал поступает через инвертор, то, когда первый триггер находится в режиме хранения, второй триггер пропускает сигнал на выход схемы. И наоборот, когда первый триггер пропускает сигнал с входа схемы на свой выход, второй триггер находится в режиме хранения.

Рисунок 4 - Временные диаграммы D-триггера,

работающего по фронту

Обратите внимание, что сигнал на выходе всей схемы в целом не зависит от сигнала на входе «D» схемы. Если первый триггер пропускает сигнал данных со своего входа на выход, то второй триггер в это время находится в режиме хранения и поддерживает на выходе предыдущее значение сигнала, то есть сигнал на выходе схемы тоже не может измениться.

В результате проведённого анализа временных диаграмм мы определили, что сигнал в схеме, приведенной на рисунке 3 запоминается только в момент изменения сигнала на синхронизирующем входе «C» с единичного потенциала на нулевой.

Динамические D триггеры выпускаются в виде готовых микросхем или входят в виде готовых блоков в составе больших интегральных схем, таких как базовый матричный кристалл (БМК) или программируемых логических интегральных схем (ПЛИС).

Иногда при изображении динамического входа указывают, по какому фронту триггер (или триггеры) изменяет своё состояние. В этом случае используется обозначение входа, как это показано на рисунке 5.

Рисунок 5 -

Обозначение динамических входов

На рисунке 5а обозначен динамический вход, работающий по переднему (нарастающему) фронту сигнала. На рисунке 5б обозначен динамический вход, работающий по заднему (спадающему) фронту сигнала.

Ход работы

1. Изучить по данному методическому указанию и другой литературе основные принципы построения D триггеров и методы их синтеза.

2. Произвести синтез статического D-триггера, в базисах И-НЕ (или ИЛИ-НЕ). Эскиз изобразить в тетради, схему на формате А4.

3. Произвести синтез динамического D-триггера, в базисах И-НЕ, (или ИЛИ-НЕ). Эскиз изобразить в тетради, схему на формате А4.

Контрольные вопросы

1. Укажите, чем отличается динамическое управление триггерами от статического управления?

2. Какие D-триггеры нашли широкое применение? Где?

3. Такие триггеры делятся на триггеры со статическим управлением и триггеры с динамическим управлением?

4. Как называется триггер, который имеет один информационный вход, один вход синхронизации и два выхода: прямой и инверсный, также называемый триггером с задержкой?

Материалы на данной страницы взяты из открытых источников либо размещены пользователем в соответствии с договором-офертой сайта. Вы можете сообщить о нарушении.