Практическое занятие № 43-44

Тема: «Синтез комбинационной логической цепи цифрового сумматора двоичных чисел»

Цель: изучение форм представления чисел в цифровых устройствах и исследование схем комбинационных цифровых устройств –сумматоров.

Теория

Сумматор является простейшим цифровым устройством, предназначенным для сложения двух чисел, заданных в двоичном коде. Сложение производиться поразрядно – от младшего разряда к старшему. В каждом разряде необходимо найти сумму Si слагаемых Хi и Yi. и переноса из предыдущего разряда Pi-1.

По числу входов различают полусумматоры, одноразрядные сумматоры и многоразрядные сумматоры.

Полусумматорами называются устройства с двумя входами и двумя выходами, на которых вырабатываются сигналы суммы и переноса. В таблице приведена таблица истинности полусумматора.

|

ai |

bi |

Si |

Сi+1 |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

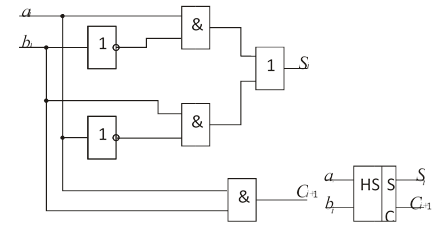

Графическая схема полусумматора с использованием базовых логических элементов приведена на рисунке

В соответствии со своим вариантом опробовать в debug и пояснить команды. Осуществить ассемблирование и дизассемблирование указанных команд.

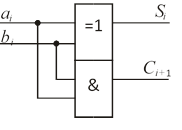

Графическая схема полусумматора с использованием логических элементов ИСКЛЮЧАЮЩЕЕ-ИЛИ, приведена на рисунке.

|

В зависимости от характера ввода-вывода кодов и организации переносов многоразрядные сумматоры бывают последовательного и параллельного принципа действия.

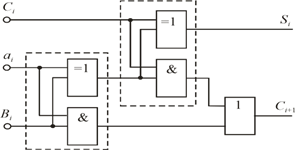

В последовательном сумматоре сложение кодов осуществляется, поразрядно начиная с младшего разряда с помощью комбинационного сумматора на три входа. Образующийся в данном разряде перенос Рj+1 задерживается на время tэд и поступает на вход Pj сумматора в момент поступления следующего разряда слагаемых. Таким образом, последовательно разряд за разрядом производиться сложение кодов чисел. Схема последовательного сумматора приведена на рисунке.

Достоинством последовательного сумматора является простота аппаратурной реализации, а недостатком – достаточно большое время суммирования.

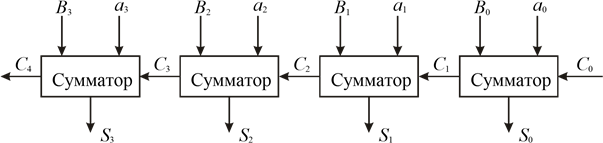

В параллельном сумматоре достигается более высокое быстродействие. Суммируемые коды поступают на входы сумматора одновременно по всем разрядам. Для этого в каждом разряде используется комбинационный сумматор на три входа, на выходах которого образуются значения суммы Sj данного разряда и переноса Pj+1 в старший разряд. В процессе распространения сигнала переноса устанавливается окончательное значение суммы в каждом разряде. Очевидно, что в течение этого времени на входах сумматора присутствуют сигналы Xi, Yi, соответствующие суммируемым кодам. Максимальное по времени суммирование получается в том случае, когда перенос, возникший в первом разряде, распространяется по всем разрядам (например, при сложении кодов 11…11 и 00...01).

Ход работы

1 Перевести десятичное число, равное вашему номеру в журнале плюс пятнадцать, в следующие системы счисления: двоичную, восьмеричную, шестнадцатеричную, двоично-десятичную (переводы производить в тетради).

2 Число, полученное в двоичном коде, перевести в обратный и дополнительный код.

3 Разработать и начертить эскиз (в тетради), схему (на формате А4) электрическую функциональную трехразрядного сумматора с последовательным переносом с использованием полусумматоров. Привести таблицу истинности.

4

Материалы на данной страницы взяты из открытых источников либо размещены пользователем в соответствии с договором-офертой сайта. Вы можете сообщить о нарушении.