Практическое занятие № 45-46

Тема: «Проектирование полного n-разрядного сумматора»

Цель: получение навыков проектирования сумматоров на уровне регистровых передач

Теория

Сумматор – это схема, которая предназначена для суммирования двух входных двоичных n-разрядных кодов. Операция вычитания заменяется сложением слов в обратном или дополнительном коде. Операции умножения и деления сводятся к реализации многократных сложений и сдвигов. Поэтому сумматор является важным компонентом любого арифметико-логического устройства.

Сумматор состоит из элементарных подсхем, которые называются одноразрядными сумматорами.

Существуют следующие классификации сумматоров:

• по числу входов:

§ полусумматоры,

§ одноразрядные сумматоры, многоразрядные сумматоры.

• по способу сложения:

§ параллельные – все разряды операндов поступают одновременно на соответствующие входы одноразрядных суммирующих схем,

§ последовательные – значения разрядов операндов и переноса, которые запомнились в предыдущем такте, поступают последовательно в направлении от младших разрядов к старшим на входы одного одноразрядного сумматора,

§ параллельно-последовательные – число разбивается на части (например, байты), разряды байтов поступают на входы подсумматоров (в нашем примере – восьмиразрядных сумматоров) параллельно (одновременно), а сами группы разрядов (байтов) – последовательно.

• по организации хранения результатов:

§ комбинационные – результат операции сложения запоминается в регистре результата,

§ накапливающие – процесс сложения объединяется с хранением результата,

§ комбинированные,

• по организации переноса между разрядами:

§ с последовательным переносом,

§ со сквозным переносом,

§ с параллельным переносом, с комбинированным переносом,

• по системе счисления:

§ позиционные (двоичные, десятичные, двоично-десятичные и т.д.), непозиционные,

• по разрядности – в зависимости от того, сколько разрядные числа могут суммироваться,

• по способу представления отрицательных чисел,

§ в обратном коде, в дополнительном коде,

• по времени сложения:

§ синхронные – это сумматоры с постоянным интервалом времени необходимым для сложения,

§ асинхронные – это сумматоры, в которых интервал времени для сложения определяется моментом фактического окончания операции.

Одноразрядные сумматоры

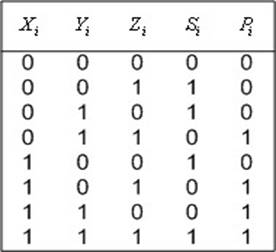

Одноразрядным сумматором называется схема, которая выполняет сложение значений разрядов Xi и Yi с учетом переноса Zi из младшего соседнего разряда и вырабатывает на выходе функцию результата Si и переноса Pi в старший соседний разряд. Исходя из этого определения таблица истинности одноразрядного сумматора будет иметь следующий вид.

Рисунок 1 - Таблица истинности для одноразрядного сумматора

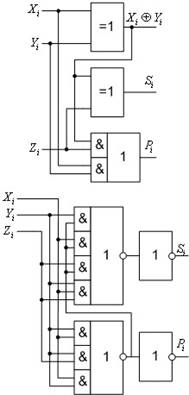

Минимизировав логическое выражение, описанное в таблице истинности, получаем следующие схемы одноразрядных сумматоров различных базисах:

а б

а б

Рисунок 2 - Схемы одноразрядных сумматоров в различных базисах: а – в базисе И-НЕ, б – с элементами ИСКЛЮЧАЮЩЕЕ ИЛИ

Последовательные сумматоры

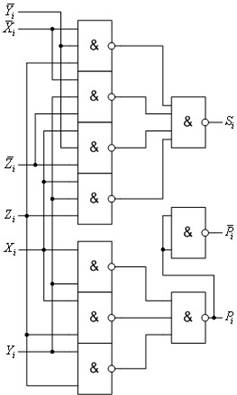

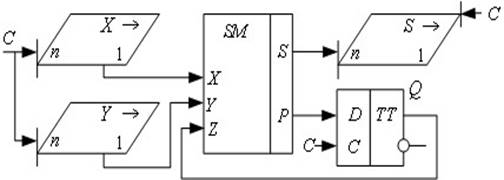

Последовательный двоичный многоразрядный сумматор включают в себя n-разрядный сдвиговые регистры операндов X и Y, регистр результата S, одноразрядный сумматор SM и двухступенчатый D-триггер для запоминания переноса. Все регистры обеспечивают одновременный сдвиг влево, в сторону младших разрядов.

Рисунок 3 - Схема последовательного многоразрядного сумматора

В последовательном сумматоре попарная передача значений разрядов Xi и Yi начинается с младших разрядов. Образуются значения суммы Si и переноса Pi , которые записываются соответственно в регистр результата и в триггер запоминания переноса на один такт Tc . Последовательное сложение выполняется за столько тактов, сколько разрядов в числе.

Для суммирования отрицательных числе удобно использовать дополнительный код второго операнда.

Последовательный сумматор требует минимальных аппаратных затрат, однако длительность операции сложения пропорциональна разрядности операндов. Поэтому последовательный сумматор можно использовать в относительно медленнодействующих устройствах.

Параллельные сумматоры

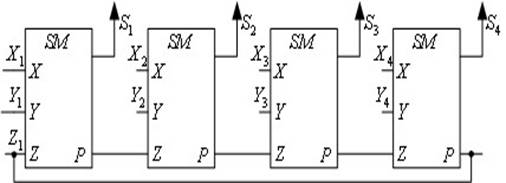

Параллельный многоразрядный сумматор содержит n одноразрядных схем сложения.

Рисунок 4 - Схема параллельного четырехразрядного сумматора

Значения всех разрядов двух чисел X и Y поступают на входы соответствующих одноразрядных сумматоров параллельно (одновременно). В параллельных сумматорах с последовательным переносом значение сигнала переноса Pi передается от разряда к разряду асинхронно. При использовании обратного кода перенос из самого старшего разряда подается на вход переноса младшего разряда по цепи циклического переноса. При использовании дополнительного кода цепь циклического переноса разрывается, а на вход переноса младшего разряда подается логический нуль.

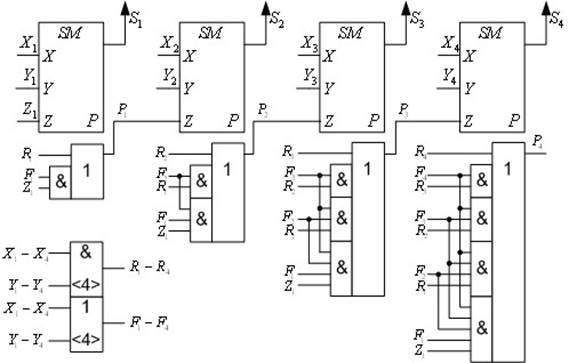

Параллельные сумматоры с параллельными переносами

Для повышения быстродействия сумматоров используют n -разрядные сумматоры с параллельными переносами. При этом сумматор разбивается на две части: собственно, схему сложения и схему выработки ускоренных переносов (СУП). Схема сложения содержит n упрощенных одноразрядных сумматоров SM на три входа и только на один выход суммы Si .

Рисунок - 5 Схема четырехразрядного сумматора с параллельными переносами

Ход работы

1. Составить схему многоразрядного сумматора согласно варианту в базисе И-НЕ или ИЛИ-НЕ.

2. Составить схему многоразрядного сумматора согласно варианту на основе одноразрядных сумматоров. Обозначит входные, выходные и управляющие сигналы.

Вариант выбрать по последней цифре в номере списка в журнале. Эскизы привести в тетради, схемы на формате А4.

Номер варианта

1. 8-разрядный последовательный сумматор

2. 8-разрядный последовательный вычитатель в обратном коде

3. 8-разрядный последовательный вычитатель в дополнительном коде

4. 6-разрядный параллельный сумматор

5. 6-разрядный параллельный вычитатель в обратном коде

6. 6-разрядный параллельный вычитатель в дополнительном коде

7. 10-разрядный последовательный сумматор

8. 10-разрядный последовательный

вычитатель в обратном коде

9. 10-разрядный последовательный

вычитатель в дополнительном коде

10. 8-разрядный параллельный сумматор

Примечание: если в варианте явно не указан какой-либо параметр сумматора, то он может выбираться студентом по его усмотрению.

Контрольные вопросы

1. Что такое сумматор?

2. Какие классификации сумматоров вам известны?

3. Какие принципиальные преимущества и недостатки имеют последовательны и параллельные сумматоры?

Скачано с www.znanio.ru

Материалы на данной страницы взяты из открытых источников либо размещены пользователем в соответствии с договором-офертой сайта. Вы можете сообщить о нарушении.