Практическое занятие № 59

Тема: «Организация памяти»

Цель: познакомиться с вариантом организации памяти на примере проектирования модуля ОЗУ

1 ПРОЕКТИРОВАНИЕ ОЗУ

1.1 Расчет параметров ОЗУ

Приведем технические требования к модулю ОЗУ (таблица 1.1).

Таблица 1.1 – Технические требования к модулю ОЗУ

|

Быстродействие |

500 нс |

|

Разрядность |

16 бит |

|

Объем памяти |

128 Кбайт |

|

Тип интерфейса |

ИК1, И-41 или МПИ |

После анализа характеристик различных микросхем памяти в качестве элемента памяти выбираем микросхему компании AMIC.

Приведем характеристики микросхемы памяти A43L8316A (таблица 1.2)

Таблица 1.2 – Характеристики микросхемы памяти A43L8316A

|

Тип ячейки памяти |

n-МОП |

|

Информационная емкость, бит |

128K |

|

Организация памяти, слов × разрядов |

128К*16 бит |

|

Время выборки адреса, нс |

16 |

|

Тип выхода |

ТТЛ |

|

Напряжение питания, В (отклонение, %) |

|

|

Тип корпуса |

TSOP |

Число БИС ЗУ, используемых в накопителе модуля, определяется по следующей формуле, и не зависит от способов построения накопителя:

![]()

где ![]() – количество чисел

(адресов) в ОЗУ;

– количество чисел

(адресов) в ОЗУ;

![]() – число разрядов в ОЗУ;

– число разрядов в ОЗУ;

![]() и

и

![]() – количество чисел и

разрядов в БИС ЗУ соответственно.

– количество чисел и

разрядов в БИС ЗУ соответственно.

![]()

В данном случае разделение ОЗУ на субмодули не требуется.

Вычислим число разрядов в регистре адреса:

![]()

Вычислим коэффициент объединения микросхем памяти по входу по адресным цепям и цепям режима:

![]()

Вычислим коэффициент объединения по информационным выходным цепям:

![]()

Вычислим коэффициент объединения по цепям выбора микросхемы:

![]()

Коэффициент

разветвления ![]() принимаем равным 10.

принимаем равным 10.

Вычислим число согласующих схем по каждой цепи. Число согласующих схем в цепи адреса:

Число согласующих схем в цепи режима:

Число согласующих схем в информационных выходных цепях:

Число согласующих схем во входных цепях:

![]()

В данном случае буферизацию адреса будут выполнять мультиплексоры. Мультиплексоры имеют высокий коэффициент разветвления по выходу и коэффициент объединения по адресным входам достаточно низкий, следовательно, схема размножения адреса не требуется.

Так как ОЗУ не разделено на субмодули, то дешифратор выбора микросхемы в данном случае не требуется.

1.2 Характеристика элементной базы модуля ОЗУ

Выберем интерфейс для обмена данных с ОЗУ. Исходными данными для выбора интерфейса являются количество адресов в ОЗУ и размер слова памяти. Для проектировки ОЗУ согласно техническим требованиям необходимо использовать 20 разрядов в шине адреса и 16 разряда в шине данных.

С учетом исходных

данных был выбран интерфейс И-41. Магистраль данного интерфейса включает в себя

двадцати одно разрядную шину адреса, двадцати четырех разрядную шину данных и

шину управления с линиями сигналов: ![]() – «запись в ОЗУ»,

– «запись в ОЗУ», ![]() – «чтение из ОЗУ»,

– «чтение из ОЗУ», ![]() – ответ «Подтверждение

обмена»,

– ответ «Подтверждение

обмена», ![]() – «Запрет ОЗУ»

(запрещает ОЗУ реагировать на адрес),

– «Запрет ОЗУ»

(запрещает ОЗУ реагировать на адрес), ![]() – «Разрешение старшего

байта» (указание о двухбайтовой передаче данных).

– «Разрешение старшего

байта» (указание о двухбайтовой передаче данных).

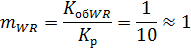

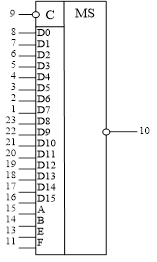

В качестве запоминающего элемента для накопителя ОЗУ была выбрана микросхема A43L8316A (цоколевка микросхемы приведена на рисунке 1.1). Данная микросхема представляет собой элемент динамической памяти.

Назначение выводов микросхемы A43L8316Aпоказано в таблице 1.3.

Таблица 1.3 – Назначение выводов микросхемы A43L8316A

|

Вывод |

Назначение |

|

/CS |

Блокирует работу устройства, включая или выключая все входы |

|

CKE |

Приостанавливает выполнение команды до следующего цикла |

|

A0~A8/AP |

Адресные выводы |

|

/RAS |

Стробирование адреса строки |

|

/CAS |

Стробирование адреса столбца |

|

/WE |

Включение записи |

|

L(U)DQM |

Переводит выход в высокоимпедансное состояние |

|

D0~D15 |

Входы/выходы данных |

|

VDD/VSS |

Блок питания для входных буферов и логического ядра |

|

VDDQ/VSSQ |

Блок питания для выходных буферов |

|

NC/RFU |

Нет подключения/Зарезервировано для будущего |

Рисунок 1.1 – Цоколевка микросхемы A43L8316A

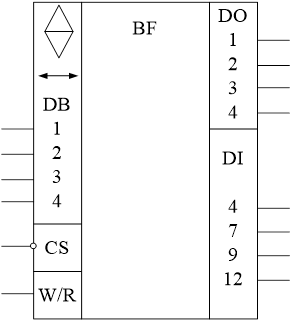

Для мультиплексирования адреса применяются микросхемы типа К155КП1. Данная микросхема представляет собой двойной мультиплексор с четырьмя входами адреса. Помимо мультиплексирования адреса микросхема К155КП1 также выполняет буферизирование содержимого шины адреса. Приведем цоколевку микросхемы К155КП1 (рисунок 1.2).

Рисунок 1.2 - Цоколевка микросхемы К155КП1

Назначение выводов микросхемы К155КП1 показано в таблице 1.4.

Таблица 1.4 – Назначение выводов микросхемы К155КП1

|

Вывод |

Назначение |

|

1~8 |

Информационные входы D7-D0 |

|

9 |

Стробирующий вход |

|

10 |

Выход |

|

11 |

Вход адресный F |

|

12 |

Общий |

|

13 |

Вход адресный E |

|

14 |

Вход адресный B |

|

15 |

Вход адресный A |

|

16~23 |

Информационные входы D15-D8 |

|

24 |

Напряжение питания |

Для осуществления обмена данных с другими устройствами в ОЗУ используются шинные формирователи (приемопередатчики). Для реализации ОЗУ был выбран четырехразрядный двунаправленный приемопередатчик К589АП16. Назначение выводов микросхемы К589АП16 показано в таблице 1.5, а на рисунке 1.3 показана цоколевка данного элемента.

Таблица 1.5 – Назначение выводов микросхемы К589АП16

|

Вывод |

Назначение |

|

DB |

Подключение к внешней (системной) шине (двунаправленная передача) |

|

DI |

Входные данные |

|

DO |

Выходные данные |

|

CS = 0 |

Разрешение передачи |

|

CS = 1 |

Все выходы в высокоимпедансном состоянии |

|

W/R = 0 |

Передача от DI к DB |

|

W/R = 1 |

Передача от DB к DO |

Рисунок 1.3 – Цоколевка микросхемы К589АП16

1.3 Описание отдельных блоков ОЗУ

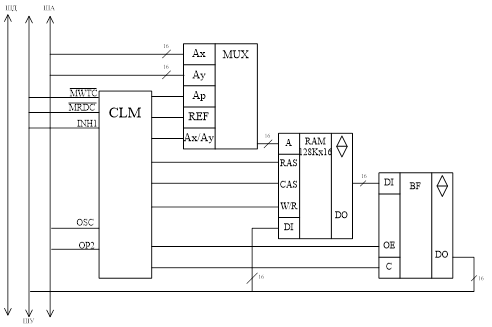

ОЗУ можно структурно разделить на четыре блока: блок запоминающих элементов, состоящий из одного модуля, контроллер ОЗУ, схема мультиплексирования адреса, блок шинных формирователей.

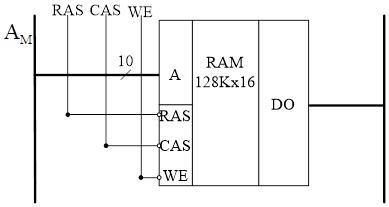

Основой ОЗУ является блок запоминающих элементов, состоящий из одного модуля. Модуль ОЗУ будет представлять собой 1 микросхему A43L8316A.

Рисунок 1.4 – Схема модуля ОЗУ

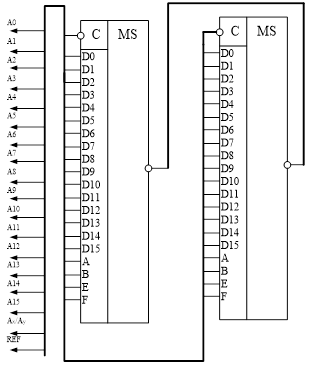

Для

мультиплексирования адреса применяется блок мультиплексоров, состоящий двух

мультиплексоров, каждый из которых расположен в отдельной микросхеме К155КП2.

На входы I1 мультиплексоров

подаются разряды адреса строки, на входы I2

– разряды адреса столбца, на входы I3-I4

– разряды адреса строки при регенерации. На вход S0

подается сигнал ![]() , на вход S1

– сигнал REF. На рисунке 1.5

приведена схема мультиплексирования.

, на вход S1

– сигнал REF. На рисунке 1.5

приведена схема мультиплексирования.

Рисунок 1.5 – Схема мультиплексирования

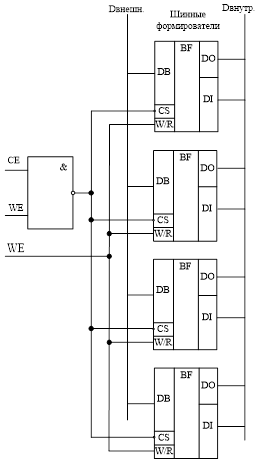

Схема шинных формирователей предназначена для приема и передачи информации в шину данных. Так как в схеме используются четырехразрядные двунаправленные приемопередатчики, то в схеме шинных формирователей их будет восемь.

Приведем схему шинных формирователей на рисунке 1.6 на следующей странице, а на этой – назначение всех его входов.

Контроллер ОЗУ

предназначен для выработки сигналов ![]() ,

, ![]() ,

, ![]() ,

, ![]() ,

, ![]() ,

, ![]() и

и

![]() , которые используются

для управления модулем памяти, блоком шинных формирователей и блоком

мультиплексирования. Входными сигналами для контроллера являются сигналы с шины

управления и сигналы от генераторной микросхемы.

, которые используются

для управления модулем памяти, блоком шинных формирователей и блоком

мультиплексирования. Входными сигналами для контроллера являются сигналы с шины

управления и сигналы от генераторной микросхемы.

Рисунок 1.6 – Схема шинных формирователей

В данном случае структура контроллера ОЗУ не раскрывается, и он представляется в виде черного ящика. На рисунке 1.7 приведена схема модуля ОЗУ.

Рисунок 1.7 – Схема модуля ОЗУ

1.4 Временные диаграммы работы модуля ОЗУ

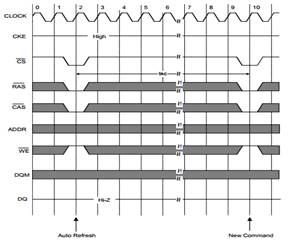

На рисунке 1.8 приведена временная диаграмма цикла регенерации.

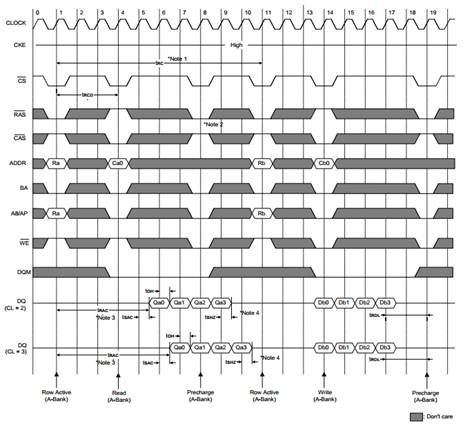

На рисунке 1.9 приведена временная диаграмма цикла чтения/записи.

Рисунок 1.8 – Временная диаграмма цикла регенерации

Рисунок 1.9 – Временная диаграмма цикла чтения/записи

Скачано с www.znanio.ru

Материалы на данной страницы взяты из открытых источников либо размещены пользователем в соответствии с договором-офертой сайта. Вы можете сообщить о нарушении.