Практическое занятие № 61

Тема: «Статическая память»

Цель: закрепить навыки по определению принципов работы статической памяти

Теория

Статическая оперативная память с произвольным доступом (SRAM — Static Random Access Memory) — полупроводниковая оперативная память, в которой каждый двоичный разряд хранится в схеме с положительной обратной связью, позволяющей поддерживать состояние сигнала без постоянной перезаписи.

Тем не менее, сохранять данные без перезаписи SRAM может только, пока есть питание, т.е. SRAM остается энергозависимым типом памяти.

Двоичная SRAM

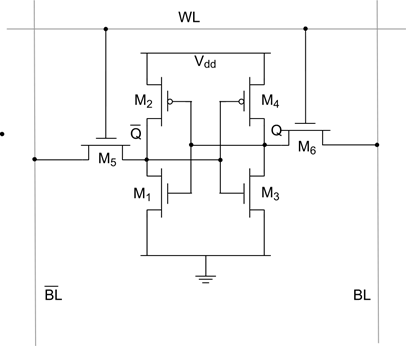

Типичная ячейка статической двоичной памяти (двоичный триггер) на КМОП-технологии состоит из двух перекрестно (кольцом) включенных инверторов и ключевых транзисторов для обеспечения доступа к ячейке.

Часто для увеличения плотности упаковки элементов на кристалле в качестве нагрузки применяют поликремниевые резисторы.

Недостатком такого решения является рост статического энергопотребления.

Рисунок 1 – Типичная ячейка статической двоичной памяти

Линия WL (Word Line) управляет двумя транзисторами доступа. Линии !BL и BL (Bit Line) – битовые линии, используются и для записи данных и для чтения данных.

Запись. При подаче «0» на линию !BL или BL параллельно включенные транзисторные пары (M5 и M1) и (M6 и M3) образуют логические схемы 2ИЛИ, последующая подача «1» на линию WL открывает транзистор M5 или M6, что приводит к соответствующему переключению триггера.

Чтение. При подаче «1» на линию WL открываются транзисторы M5 и M6, уровни записанные в триггере выставляются на линии !BL и BL, и попадают на схемы чтения.

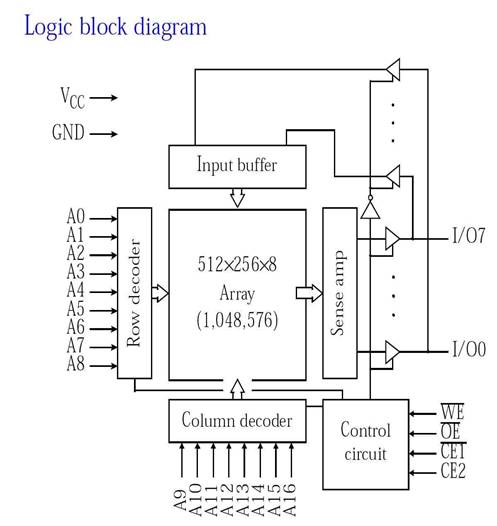

Для выбора ячеек (WL) используются дешифратор адреса.

Рисунок 2 – Дешифратор адреса

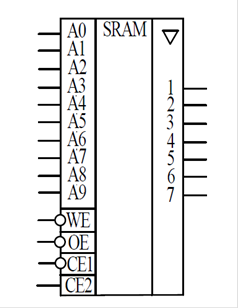

Рисунок 3 – Условно-графическое обозначение микросхем SRAM

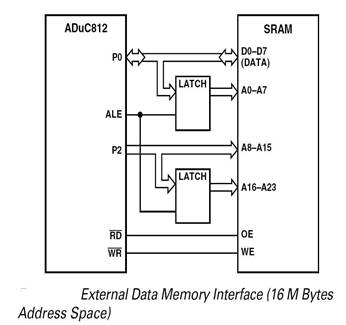

Рисунок 4 – Пример подключения SRAM к микроконтроллеру

Преимущества:

− Быстрый доступ. SRAM — это действительно память произвольного доступа, доступ к любой ячейке памяти в любой момент занимает одно и то же время.

− Простая схемотехника — SRAM не требуются сложные контроллеры.

− Возможны очень низкие частоты синхронизации, вплоть до полной остановки синхроимпульсов.

− Недостатки:

− Невысокая плотность записи (шесть элементов на бит, вместо двух у DRAM).

− Высокое энергопотребление.

Вследствие чего — дороговизна килобайта памяти.

Тем не менее, высокое энергопотребление не является принципиальной особенностью SRAM, оно обусловлено высокими скоростями обмена с данным видом внутренней памяти процессора.

Энергия потребляется только в момент изменения информации в ячейке SRAM.

Применение

SRAM применяется в микроконтроллерах и ПЛИС, в которых объем ОЗУ невелик (единицы килобайт), зато нужны низкое энергопотребление (за счет отсутствия сложного контроллера динамической памяти), предсказываемое с точностью до такта время работы подпрограмм и отладка прямо на устройстве.

− В устройствах с большим объемом ОЗУ рабочая память выполняется как DRAM.

− SRAM’ом же делают регистры и кэш-память.

Скачано с www.znanio.ru

Материалы на данной страницы взяты из открытых источников либо размещены пользователем в соответствии с договором-офертой сайта. Вы можете сообщить о нарушении.