Практическое занятие № ____

Тема: Изучение состава и принципа действия памяти Цель: закрепить навыки по определению принципов работы динамической памяти.

Ход работы:

1. Дайте характеристику DRAM: преимущества и недостатки, принцип организации работы, характеристики

2. Привести сравнительную характеристику ОЗУ FPM, EDO, BEDO, VRAM, SDRAM ESDRAM, DDR SDRAM, RDRAM в таблице 1

|

|

FPM |

EDO |

BEDO |

VRAM |

SDRAM |

ESDRAM |

DDR SDRAM |

RDRAM |

|

Наименование |

|

|

|

|

|

|

|

|

|

Производительность |

|

|

|

|

|

|

|

|

|

Особенности |

|

|

|

|

|

|

|

|

3. Охарактеризуйте модули SIMM, DIMM и RIMM 4. Какие модули памяти используются в современных ПК Выводы.

По результатам выполнения практической работы должен быть составлен отчет, который должен содержать:

• название и цель работы;

• формулировки практических заданий;

• заполненные пронумерованные и названные таблицы; выводы по практической работе; ответы на контрольные вопросы. Вопросы для самопроверки:

1. Чем представлена в ПК память DRAM?

2. Из чего состоят ячейки памяти в DRAM?

3. Дайте понятие регенерации памяти.

4. Как происходит чтение из памяти DRAM?

5. Как происходит запись в память DRAM?

6. В чем достоинства и недостатки памяти FPM?

7. В чем достоинства и недостатки памяти EDO/ВEDO?

8. В чем достоинства и недостатки памяти SDRAM?

9. В чем достоинства и недостатки памяти DDR SDRAM?

10. Какие модули памяти используются в современных ПК?

Методические указания:

Динамическая оперативная память (Dynamic RAM – DRAM) используется в большинстве систем оперативной памяти персональных компьютеров. Основное преимущество этого типа памяти состоит в том, что ее ячейки упакованы очень плотно, т.е. в небольшую микросхему можно упаковать много битов, а значит, на их основе можно построить память большей емкости.

Ячейки памяти в микросхеме DRAM – это крошечные конденсаторы, которые удерживают заряды. Проблемы, связанные с памятью этого типа, вызваны тем, что она динамическая, т.е. должна постоянно регенерироваться, так как в противном случае электрические заряды в конденсаторах памяти будут «стекать», и данные будут потеряны. Регенерация в микросхеме происходит одновременно по всей строке матрицы при обращении к любой из ее ячеек. Максимальный период обращения к каждой строке TRF (refresh time) для гарантированного сохранения информации у современной памяти лежит в пределах 8-64 мс. В зависимости от объема и организации матрицы для однократной регенерации всего объема требуется 512, 1024, 2048 или 4096 циклов обращений. При распределенной регенерации (distributed refresh) одиночные циклы регенерации выполняются равномерно с периодом tRF, который для стандартной памяти принимается равным 15,6 мкс. Период этих циклов называют «refresh rate», хотя такое название больше подошло бы к обратной величине – частоте циклов f=l/tRF. Для памяти с расширенной регенерацией (extended refresh) допустим период циклов до 125 мкс. Возможен также и вариант пакетной регенерации (burst refresh), когда все циклы регенерации собираются в пакет, во время которого обращение к памяти по чтению и записи блокируется. При количестве циклов 1024 эти пакеты будут периодически занимать шину памяти примерно на 130 мкс, что далеко не всегда допустимо. По этой причине, как правило, выполняется распределенная регенерация, хотя возможен и промежуточный вариант – пакетами по несколько циклов.

В устройствах DRAM для хранения одного бита используется только транзистор и конденсатор, поэтому они более вместительны, чем микросхемы других типов памяти. Транзистор для каждого однозарядного регистра DRAM использует для чтения состояния смежного конденсатора. Если конденсатор заряжен, в ячейке записана 1; если заряда нет – записан 0. Заряды в крошечных конденсаторах все время стекают, вот почему память должна постоянно регенерироваться. Даже мгновенное прерывание подачи питания или какой-нибудь сбой в циклах регенерации приведет к потере заряда в ячейке DRAM, а следовательно, к потере данных.

Каждая ячейка способна хранить только один бит. Если конденсатор ячейки заряжен, то это означает, что бит включен, если разряжен – выключен. Если необходимо запомнить один байт данных, то понадобится 8 ячеек (1 байт = 8 битам). Ячейки расположены в матрицах и каждая из них имеет свой адрес, состоящий из номера строки и номера столбца. Структура ячеек памяти DRAM представлена на рисунке 1.

Теперь рассмотрим, как происходит чтение. Сначала на все входы подается сигнал RAS (Row Address Strobe) – это адрес строки. После этого, все данные из этой строки записываются в буфер. Затем на регистр подается сигнал CAS (Column Address Strobe) – это сигнал столбца и происходит выбор бита с соответствующим адресом. Этот бит и подается на выход. Но во время считывания данные в ячейках считанной строки разрушаются и их необходимо перезаписать, взяв из буфера.

Теперь запись. Подается сигнал WR (Write) и информация поступает на шину столбца не из регистра, а с информационного входа памяти через коммутатор, определенный адресом столбца. Таким образом, прохождение данных при записи определяется комбинацией сигналов адреса столбца и строки и разрешения записи данных в память. При записи данные из регистра строки на выход не поступают.

Следует учесть то, что матрицы с ячейками расположены вот таким вот образом (рисунок 2).

|

Рисунок 1 – Структура ячеек памяти DRAM |

Рисунок 2 – Расположение ячеек матрицы |

Это означает, что за один раз будет считан не один бит, а несколько. Если параллельно расположено 8 матриц, то сразу считан будет один байт. Это называется разрядностью. Количество линий, по которым будут передаваться данные от (или на) параллельных матриц, определяется разрядностью шины ввода/вывода микросхемы.

Важнейшей характеристикой DRAM является быстродействие, а проще говоря, продолжительность цикла + время задержки + время доступа, где продолжительность цикла – время, затраченное на передачу данных, время задержки – начальная установка адреса строки и столбца, а время доступа – время поиска самой ячейки. Измеряется в наносекундах.

Сейчас уже не актуально использовать 66-МГц шины памяти. Разработчики DRAM нашли возможность преодолеть этот рубеж и извлекли некоторые дополнительные преимущества путем осуществления синхронного интерфейса. С асинхронным интерфейсом процессор должен ожидать, пока DRAM закончит выполнение своих внутренних операций, которые обычно занимают около 60 нс. С синхронным управлением DRAM происходит защелкивание информации от процессора под управлением системных часов. Триггеры запоминают адреса, сигналы управления и данных, что позволяет процессору выполнять другие задачи. После определенного количества циклов данные становятся доступны, и процессор может считывать их с выходных линий.

Другое преимущество синхронного интерфейса заключается в том, что системные часы задают только временные границы, необходимые DRAM. Это исключает необходимость наличия множества стробирующих импульсов. В результате упрощается ввод, т. к. контрольные сигналы адреса данных могут быть сохранены без участия процессора и временных задержек. Подобные преимущества также реализованы и в операциях вывода.

FPM FPM (Fast Page Mode) DRAM – динамическое ОЗУ, работающее в режиме ускоренного страничного обмена

Тип динамической памяти с произвольным доступом, которая обеспечивает более высокую производительность, чем обычное динамическое ОЗУ.

Двоичные разряды хранятся в ячейках памяти, организованных в виде матрицы, состоящей из строк и столбцов. Подобно всем остальным видам динамического ОЗУ, у ИС памяти данного типа имеется лишь половина всех выводов, необходимых для указания адреса чтения или записи данных. При этом цикл памяти начинается с указания в первую очередь адреса строки, для чего требуется половина разрядов адреса, а затем и адреса столбца данных, который составляет другую половину адреса. Затем выполняется чтение или запись данных.

Режим ускоренного страничного обмена позволяет адресовать следующий столбец, который соответствует следующему по порядку адресу памяти, без повторного указания строки. Это дает возможность сократить время доступа к нескольким следующим по порядку ячейкам памяти при условии, что при этом еще не достигнут конец строки, увеличивая тем самым производительность.

Время цикла памяти FPM DRAM составляет 50нс, что позволяет поддерживать доступ к памяти с частотой 30 миллионов раз в секунду или 30 МГц. Этого вполне достаточно для шины памяти с тактовой частотой 60 или 66 МГц, типичной для процессора Pentium. Следовательно, для доступа к памяти требуется не один цикл памяти, причем это делается в пакетном режиме, поэтому адреса памяти отнюдь не обязательно указывать при каждом доступе. Это возможно потому, что доступ к памяти обычно осуществляется в виде обращения к расположенным по порядку ячейкам памяти, а если это не так, то дополнительный доступ к памяти не используется либо данные игнорируются. Доступ к памяти в пакетном режиме обычно обозначается формулой 6-3-3-3, которая означает, что для первого обращения к памяти требуется 6 тактовых циклов, поскольку при этом необходимо полностью указать адрес, а для каждого из трех последующих обращений требуется лишь 3 тактовых цикла. Как правило, тактовые циклы выполняются с быстродействием шины памяти процессора. Зачастую это соответствует тактовой частоте 60 или 66 МГц при внутренней тактовой частоте процессора соответственно 120 или 133 МГц.

Память FPM была распространена в ПК в 1995 году. Более быстродействующим типом памяти является динамическое ОЗУ EDO DRAM.

EDO Начиная с 1995 года, в компьютерах на основе Pentium используется новый тип оперативной памяти – EDO ( Extended Data Out). Это усовершенствованный тип памяти FPM; его иногда называют Hyper Page Mode. Память типа EDO была разработана и запатентована фирмой Micron Tehnology. Память EDO собирается из специально изготовленных микросхем, которые учитывают перекрытие синхронизации между очередными операциями доступа.

Не смотря на небольшие конструктивные различия, и FPM, и EDO RAM делаются по одной и той же технологии, поэтому скорость работы должна быть одна и та же. Действительно, и FPM, и EDO RAM имеют одинаковое время считывания первой ячейки – 60 – 70 нс. Однако в EDO RAM применен метод считывания последовательных ячеек. При обращении к EDO RAM активизируется не только первая, но и последующие ячейки в цепочке. Поэтому, имея то же время при обращении к одной ячейке, EDO RAM обращается к следующим ячейкам в цепочке значительно быстрее. Поскольку обращение к последовательно следующим друг за другом областям памяти происходит чаще, чем к ее различным участкам (если отсутствует фрагментация памяти), то выигрыш в суммарной скорости обращения к памяти значителен.

BEDO Двукратное увеличение производительности было достигнуто в BEDO DRAM (Burst

EDO). Добавив в микросхему генератор номера столбца, конструкторы ликвидировали задержку

CAS Delay, сократив время цикла до 15 нс. После обращения к произвольной ячейке микросхема BEDO автоматически, без указаний со стороны контроллера, увеличивает номер столбца на единицу, не требуя его явной передачи. По причине ограниченной разрядности адресного счетчика (конструкторы отвели под него всего лишь два бита) максимальная длина пакета не могла превышать четырех ячеек (22=4). Все же, несмотря на свои скоростные показатели, BEDO оказалась не конкурентоспособной и не получила практически никакого распространения. Просчет состоял в том, что BEDO, как и все ее предшественники, оставалась асинхронной памятью. Это накладывало жесткие ограничения на максимально достижимую тактовую частоту, ограниченную 60 - 66 (75) мегагерцами.

VRAM VRAM (Video Random Access Memory) –Видео ОЗУ. Память, специально адаптированная для использования в видеоадаптерах. Двухпортовая память – ПК может записывать данные (для изменения изображения) в то время, когда видеоадаптер непрерывно считывает содержимое VRAM для прорисовки его на экране. Обычно необходимость в памяти такого типа возникает при работе с высокими разрешениями (более 1024 х 768 пикселов) в «глубоком» цвете (более 65536 цветов) и высокой частотой кадровой развертки (более 85 Гц). «Оконное» ОЗУ (WRAM - Window RAM) также является двухпортовой, однако поддерживает более эффективную схему буферизации и другие усовершенствования, позволяющие повысить производительность на 25% по сравнению с VRAM. Оба описанных типа ОЗУ производительнее и дороже EDO.

SDRAM SDRAM (Synchronous Dynamic Random Access Memory) – это синхронизированная динамическая память с произвольным порядком выборки. Одним словом, синхронная динамическая оперативная память. SDRAM состоит из физических ячеек, которые собраны в страницы. Размер страницы может быть от 512 байт до нескольких килобайт. Каждая страница разбита на два банка: в одном банке ячейки с нечетными адресами строк, а в другом – с четными. Каждая ячейка имеет свой адрес, состоящий из номера (адреса) строки и номера (адреса) столбца. Сначала передается номер строки, затем номер столбца. По сути дела, номер – это набор электрических сигналов, которые надо сгенерировать, передать и обработать. На все это необходимо затратить время. В страничном режиме, передав номер строки можно получить доступ к нескольким ячейкам с разными номерами столбцов, то есть, не надо для каждой из них передавать номер строки, достаточно только номера столбца. Экономия времени налицо. Двигаемся дальше, строки можно разделить на четные и нечетные. Получается два банка: один – с четными строками, а другой – с нечетными. В то время, когда происходит обращение к одному банку, в другом происходит выборка адреса или еще что. Опять же экономия времени. Такой режим иногда называют расслоением.

Для того чтобы увеличить скорость доступа к памяти, разработали пакетный режим (burst) доступа. Принцип состоит в том, что после установки строки и столбца ячейки, происходит обращение к следующим трем смежным адресам без дополнительных состояний ожидания. Схема пакетного режима будет выглядеть так: x-y-y-y, где х – время выполнения первой операции доступа состоящей из продолжительности цикла и времени ожидания, а y – это число циклов, необходимое для выполнения каждой последующей операции. Например, для SDRAM схема будет выглядеть так: 5-1-1-1. По отдельной линии передается синхронизирующий сигнал, по шине управления передается команда, скажем на считывание. После этого формируется адрес и по шине адреса передается в память. Затем начинается передача информации по шине данных. В этот момент может быть сформирован и передан новый адрес. И так постоянно.

Enhanced SDRAM (ESDRAM) Enhanced SDRAM (ESDRAM - улучшенная SDRAM) - более быстрая версия SDRAM, сделанная в соответствии со стандартом JEDEC компанией Enhanced Memory Systems. С точки зрения времени доступа производительность ESDRAM в два раза выше по сравнению со стандартной SDRAM. В большинстве приложений ESDRAM, благодаря более быстрому времени доступа к массиву SDRAM и наличию кэша, обеспечивает даже большую производительность, чем DDR SDRAM.

Более высокая скорость работы ESDRAM достигается за счет дополнительных функций, которые используются в архитектуре этой памяти. ESDRAM имеет строку кэш-регистров (SRAM), в которых хранятся данные, к которым уже было обращение. Доступ к данным в строке кэша осуществляется быстрее, чем к ячейкам SDRAM, со скоростью 12 ns, т.к. не требуется обращаться к данным в строке через адрес в колонке. При этом скорость работы ячеек ESDRAM составляет 22 ns в отличие от стандартной скорости работы ячеек SDRAM, имеющей значения 50 - 60 ns.

При этом стоит заметить, что память ESDRAM полностью совместима со стандартной памятью JEDEC SDRAM на уровне компонентов и модулей, по количеству контактов и функциональности. Однако чтобы использовать все преимущества этого типа памяти, необходимо использовать специальный контроллер (чипсет).

Увеличение производительности при использовании ESDRAM достигается за счет применения двухбанковой архитектуры, которая состоит из массива SDRAM и SRAM строчных регистров (кэш). Строчные регистры вместе с быстрым массивом SDRAM обеспечивают более быстрый доступ для чтения и записи данных по сравнению со стандартной SDRAM. ESDRAM может работать в режиме «упреждающего обращения» к массиву SDRAM, в результате следующий цикл записи или чтения может начаться в момент, когда выполнение текущего цикла не завершено. Возможность использовать такой режим напрямую зависит от центрального процессора, управляющего работой конвейера адресации.

DDR SDRAM (SDRAM II) DDR SDRAM (Double Data Rate Synchronous Dynamic Random

Access Memory) – динамическая синхронизированная память с произвольным порядком выборки и удвоенной передачей данных. Появился этот тип памяти где-то в 1998 году и был сразу взят на вооружение производителями видеокарт. Затем DDR широко распространилась и на материнские платы. На сегодняшний день, этот тип памяти, пожалуй, наиболее применяемый в персональных компьютерах. Ведь DDR сочетает в себе приемлемую скорость и при этом относительную дешевизну. Модуль DDR SDRAM представлен на рисунке 3.

Принцип работы DDR SDRAM очень схож с обычной SDRAM (отсюда и второе название DDR SDRAM – SDRAM 2). Память разбита на страницы, каждая страница разбита на банки. Работа памяти синхронизирована с тактовым генератором системной платы. Основное отличие заключается в том, что за один цикл происходит два обращения к данным: по фронту и срезу импульса тактового сигнала системной шины. Говоря простым языком, чтение/запись происходит два раза за один такт. Кроме того, частота работы повышается за счет применения интерфейсных логических схем с еще более пониженным уровнем питания. Если для SDRAM обычно используются схемотехнические решения на базе LVTTL (Low Volt Transistor-to-Transistor Logic) с напряжением питания 3,3 В, то в DDR SDRAM - на базе SSTL (Stub Series Terminated Logic) с напряжением 2,5 В (а в перспективе и SSTL-2 с напряжением 1,25 В).

RDRAM (Rambus DRAM) Direct Rambus DRAM – это высокоскоростная динамическая память с произвольным доступом, разработанная Rambus, Inc. Она обеспечивает высокую пропускную способность по сравнению с большинством других DRAM. Direct Rambus DRAMs представляет интегрированную на системном уровне технологию.

Технология Direct Rambus представляет собой третий этап развития памяти RDRAM. Впервые память RDRAM появилась в 1995 г., работала на частоте 150 МГц и обеспечивала пропускную способность 600 Мбайт/с. Она использовалась в станциях SGI Indigo2 IMPACTtm, в приставках Nintendo64, а также в качестве видеопамяти. Следующее поколение RDRAM появилось в 1997 г. под названием Concurrent RDRAM. Новые модули были полностью совместимы с первыми. Но за год до этого события в жизни компании произошло не менее значимое событие. В декабре 1996 г. Rambus, Inc. и Intel Corporation объявили о совместном развитии памяти RDRAM и продвижении ее на рынок персональных компьютеров. Вопреки распространенному мнению, ее архитектура довольно прозаична и не блещет новизной. Основных отличий от памяти предыдущих поколений всего три:

а) увеличение тактовой частоты за счет сокращения разрядности шины,

б) одновременная передача номеров строки и столба ячейки,

в) увеличение количества банков для усиления параллелизма.

Повышение тактовой частоты вызывает резкое усиление всевозможных помех и в первую очередь электромагнитной интерференции, интенсивность которой в общем случае пропорциональна квадрату частоты, а на частотах свыше 350 мегагерц вообще приближается к кубической. Это обстоятельство налагает чрезвычайно жесткие ограничения на топологию и качество изготовления печатных плат модулей микросхемы, что значительно усложняет технологию производства и себестоимость памяти. С другой стороны, уровень помех можно значительно понизить, если сократить количество проводников, т.е. уменьшить разрядность микросхемы. Именно по такому пути компания Rambus и пошла, компенсировав увеличение частоты до 400 MHz (с учетом технологии DDR эффективная частота составляет 800 MHz) уменьшением разрядности шины данных до 16 бит (плюс два бита на ECC). Модули памяти RDRAM представлены на рисунке 4.

|

|

Рисунок 4 – Модули памяти RDRAM |

Второе (по списку) преимущество RDRAM - одновременная передача номеров строки и столбца ячейки при ближайшем рассмотрении оказывается вовсе не преимуществом, конструктивной особенностью. Это не уменьшает латентности доступа к произвольной ячейке (т.е. интервалом времени между подачей адреса и получения данных), т.к. она, латентность, в большей степени определяется скоростью ядра, а RDRAM функционирует на старом ядре.

Большое количество банков позволяет (теоретически) достичь идеальной конвейеризации запросов к памяти, несмотря на то, что данные поступают на шину лишь спустя 40 нс. после подачи запроса (что соответствует 320 тактам в 800 MHz системе), сам поток данных непрерывен.

DIP-корпус – это исторически сама древняя реализация DRAM. DIP-корпус соответствует стандарту IC. Обычно это маленький черный корпус из пластмассы, по обеим сторонам которого располагаются металлические контакты

Микросхемы динамического ОЗУ устанавливаются так называемыми банками. Банки бывают на 64, 256 Кбайт, 1 и 4 Мбайт. Каждый банк состоит из девяти отдельных одинаковых чипов. Из них восемь чипов предназначены для хранения информации, а девятый чип служит для проверки четности остальных восьми микросхем этого банка. Чипы памяти бывают одно и четырехразрядными, и иметь емкость 64 Кбит, 256 Кбит, 1 и 4 Мбит.

Одной из незаслуженно забытых конструкций модулей памяти являются SIPP-модули. Эти модули представляют собой маленькие платы с несколькими напаянными микросхемами DRAM. SIPP является сокращением слов Single Inline Package. SIPP-модули соединяются с системной платой с помощью контактных штырьков. Под контактной колодкой находятся 30 маленьких штырьков, которые вставляются в соответствующую панель системной платы. Модули SIPP имели определенные вырезы, которые не позволяли вставить их в разъемы неправильным образом.

SIMM, DIMM и RIMM В большинстве современных компьютеров вместо отдельных микросхем памяти используются модули SIMM или DIMM, представляющие собой небольшие платы, которые устанавливаются в специальные разъемы на системной плате или плате памяти. Отдельные микросхемы так припаены к плате модуля SIMM или DIMM, что выпаить и заменить их практически невозможно. При появлении неисправности приходится заменять весь модуль. По существу, модуль SIMM или DIMM можно считать одной большой микросхемой.

В РС совместимых компьютерах применяются в основном два типа модулей SIMM: 30контактные (9разрядов) и 72-контактные (36 разрядов). Первые из них меньше по размерам. Микросхемы в модулях SIMM могут устанавливаться как на одной, так и на обеих сторонах платы. Использование 30-контактных модулей неэффективно, поскольку для заполнения одного банка памяти новых 64-разрядных систем требуется восемь таких модулей. 72-пиновые разъемы SIMM ожидает та же участь, которая несколькими годами раньше постигла их 30-пиновых предшественников: те уже давно не производятся. Им на смену в 1996 г. пришел новый разъем DIMM со 168 контактами, а после и разъем RIMM. Если на SIMM реализовывались FPM и EDO RAM, то на DIMM более современная технология SDRAM. В системную плату модули SIMM необходимо было вставлять только попарно, а DIMM можно выбрать по одному, что связано с разрядностью внешней шины данных процессоров Pentium. Такой способ установки предоставляет больше возможностей для варьирования объема оперативной памяти.

Первоначально материнские платы поддерживали оба разъема, но уже довольно продолжительное время они комплектуются исключительно разъемами DIMM. Это связано с упомянутой возможностью устанавливать их по одному модулю и тем, что SDRAM обладает большим быстродействием по сравнению с FPM и EDORAM.

Если для FPM и EDO памяти указывается время чтения первой ячейки в цепочке (время доступа), то для SDRAM указывается время считывания последующих ячеек. Цепочка - несколько последовательных ячеек. На считывание первой ячейки уходит довольно много времени (60-70 нс) независимо от типа памяти, а вот время чтения последующих сильно зависит от типа.

В качестве оперативной памяти также используются модули RIMM, SO-DIMM и SO-RIMM. Все они имеют разное количество контактов. Модули SIMM сейчас встречаются только в старых моделях материнских плат, а им на смену пришли 168-контактные DIMM. Модули SO-DIMM (рисунок 26) и SO-RIMM, имеющие меньшее количество контактов, чем стандартные DIMM и RIMM, широко используются в портативных устройствах.

При установке совпадение форм-факторов модуля и разъема не всегда стопроцентно гарантирует работоспособность модуля. Для сведения к минимуму риска использования неподходящего устройства применяются так называемые ключи. В модулях памяти такими ключами являются один или несколько вырезов. Этим вырезам на разъеме соответствуют специальные выступы. Так в модулях DIMM (рисунок 27) используется два ключа. Один из них (вырез между 10 и 11 контактами) отвечает за буферизованность модуля (модуль может быть буферизованным или небуферизованным), а второй (вырез между 40 и 41 контактами) - за рабочее напряжение (может быть 5 В или 3,3 В).

Использование модулей памяти с покрытием контактов, отличным от покрытия контактов разъема также допускается. Хотя утверждают, что материал, используемый для покрытия модулей и разъемов, должен совпадать. Мотивируется это тем, что при различных материалах возможно появление гальванической коррозии, и, как следствие, разрушение модуля. Хотя такое мнение не лишено оснований, но, как показывает опыт, использование модулей и разъемов с разным покрытием никак не сказывается на работе компьютера.

Модули RIMM (Rambus Interface Memory Module), по форме похожие на обычные модули памяти, специально предназначены для памяти RDRAM. У них 30-проводная шина проходит вдоль модуля слева направо, и на эту шину без ответвлений напаиваются микросхемы RDRAM в корпусах BGA. Модуль RIMM содержит до 16 микросхем RDRAM, которые всеми выводами (кроме двух) соединяются параллельно. Микросхемы памяти закрыты пластиной радиатора. В отличие от SIMM и DIMM, у которых объем памяти кратен степени числа 2, модули RIMM могут иметь более равномерный ряд объемов — в канал RDRAM память можно добавлять хоть по одной микросхеме.

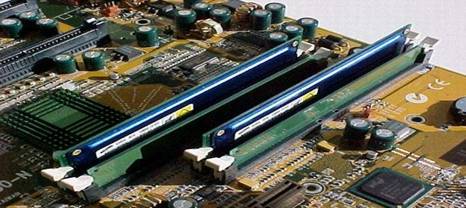

Существует много фирм, производящих чипы и модули памяти. Их можно разделить на brandname и generic-производителей. Модули памяти, вставленные в материнскую плату, представлены на рисунке 5.

Рисунок 5 – 4 - модуля памяти, вставленные в материнскую плату

При покупке хорошо бы лишний раз убедиться в правильности предоставляемой продавцом информации. Произвести такую проверку можно расшифровав имеющуюся на чипе строку букв и цифр (как правило, самую длинную) с помощью соответствующего databook и материалов, находящихся на сайте производителя. Но часто бывает, что необходимой информации не оказывается под рукой. И все же своей цели можно добиться, т. к. большинство производителей придерживаются более или менее стандартного вида предоставления информации (исключение составляют Samsung и Micron). По маркировке чипа можно узнать производителя, тип памяти, рабочее напряжение, скорость доступа, дату производства и др.

Материалы на данной страницы взяты из открытых источников либо размещены пользователем в соответствии с договором-офертой сайта. Вы можете сообщить о нарушении.