Цель занятия:

Дидактическая: сформировать основные понятия об оперативной памяти компьютера; объяснить сущность используемых терминов. Объяснить особенности работы и использования статической и динамической памяти.

Воспитательная: воспитывать интерес к будущей профессии.

План

1 Оперативная память компьютера. Организация статической и динамической памяти компьютера.

2 Организация доступа к оперативной памяти.

3 Асинхронная динамическая память.

4 Синхронная динамическая память.

5 Контрольные вопросы.

1 Оперативная память компьютера. Организация статической и динамической памяти компьютера.

В современной компьютерной системе используется память различных типов: статическая (SRAM), динамическая (DRAM), постоянная память (ROM), перепрограммируемая постоянная память (EEPROM) и некоторые другие виды памяти.

Но, основной памятью компьютера, определяющей всю его работу, является оперативная память – ОЗУ (RAM – Random Access Memory).

Главное требование к памяти:

- максимальный объем

- максимальное быстродействие

- максимальная надежность

Первоначально оперативная память была статического типа. Ячейка ОЗУ строилась на базе транзисторного каскада, который мог содержать до 10 транзисторов. Быстродействие у статической памяти было высокое, поскольку время переключения транзисторов из одного состояния в другое очень мало. Однако, такое количество транзисторов в расчете на одну ячейку памяти занимало довольно большой физический объем, т.е., интегрировать большой объем памяти в малое физическое пространство оказалось невозможным. Второй особенностью статического массива памяти стал тот факт, что транзисторы потребляют относительно большой уровень энергии, что также накладывает свои ограничения на максимальный объем памяти.

Указанных выше недостатков лишена динамическая память, ячейка которой состоит из конденсатора и управляющего транзистора. Когда конденсатор заряжен – это одно логическое состояние, когда разряжен – другое. Двух состояний вполне достаточно, поскольку компьютерная система работает с двоичным кодом (сигнал либо есть – логическая «1», либо сигнала нет – логический «0»). Конденсатор и транзистор занимают места гораздо меньше, чем несколько транзисторов. Энергопотребление такого тандема тоже гораздо ниже. Но, с быстродействием возникают проблемы. Тут причин несколько:

- разряд/заряд конденсатора – процесс более длительный, чем простое переключение транзистора;

- у конденсатора существует ток утечки, который тем больше (в относительных единицах), чем меньше емкость конденсатора.

Поэтому, для нормальной работы динамической памяти требуется периодическая регенерация памяти (подзаряд конденсаторов), что усложняет электрическую схему работы динамической памяти.

Но, поскольку, основополагающим требованием для оперативной памяти является ее объем, то динамическая память оказалась предпочтительней, несмотря на то, что она работает медленнее и имеет сложную схему управляющего контроллера.

Статическая память нашла свое применение в кэш-памяти, которая располагается непосредственно на кристалле центрального процессора, имеет невысокий объем (десятки-сотни Кб), но очень высокое быстродействие, соизмеримое с быстродействием самого процессора.

2 Организация доступа к оперативной памяти.

Компьютер работает с двоичной системой счисления (логический 0 и 1). Следовательно, и ячейка памяти может находиться в двух состояниях. Для динамической памяти конденсатор ячейки памяти может быть либо заряжен, либо разряжен.

Ячейки памяти организованы в виде матрицы, содержащей определенное количество строк и столбцов, кратных двойке в целой степени, например:

1024 – 210;

2048 – 211;

8192 – 213 и т.д.

Матрицу памяти размером 1024х1024 (1024 строки и 1024 столбца) можно описать, как 210х210. Но, чтобы упростить запись, принято указывать только степени: 10х10.

|

Измерения в байтах |

||

|

ГОСТ 8.417—2002 |

Приставки СИ |

Приставки МЭК |

|

Название |

Обозначение |

Степень |

Название |

Степень |

Название |

Символ |

Степень |

|

|

байт |

Б |

100 |

— |

|

байт |

B |

Б |

20 |

|

килобайт |

кбайт |

103 |

кило- |

103 |

кибибайт |

KiB |

КиБ |

210 |

|

мегабайт |

Мбайт |

106 |

мега- |

106 |

мебибайт |

MiB |

МиБ |

220 |

|

гигабайт |

Гбайт |

109 |

гига- |

109 |

гибибайт |

GiB |

ГиБ |

230 |

|

терабайт |

Тбайт |

1012 |

тера- |

1012 |

тебибайт |

TiB |

ТиБ |

240 |

|

петабайт |

Пбайт |

1015 |

пета- |

1015 |

пебибайт |

PiB |

ПиБ |

250 |

|

эксабайт |

Эбайт |

1018 |

экса- |

1018 |

эксбибайт |

EiB |

ЭиБ |

260 |

|

зеттабайт |

Збайт |

1021 |

зетта- |

1021 |

зебибайт |

ZiB |

ЗиБ |

270 |

|

иоттабайт |

Ибайт |

1024 |

иотта- |

1024 |

йобибайт |

YiB |

ЙиБ |

280 |

Матрица памяти может быть симметричной (количество строк и столбцов одинаково) и ассиметричной (количество строк и столбцов различно).

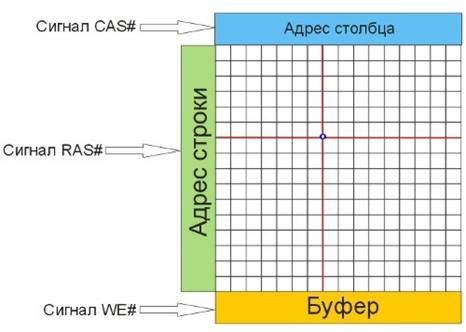

Для доступа к ячейкам памяти используется страничная адресация (Page Mode – PM). Суть ее в следующем: на адресные входы матрицы памяти последовательно подается сначала адрес строки, а затем, – адрес столбца. На пересечении конкретной строки и конкретного столбца находится конкретная ячейка памяти, содержащая конкретную информацию (0 или 1).

Рисунок 1 – Обращение к ячейке динамической памяти

Адрес строки устанавливается по низкому уровню (о чем свидетельствует значок #) управляющего сигнала RAS# (Row Address Strobe), адрес столбца – по низкому уровню сигнала CAS# (Column Address Strobe). Когда выбраны конкретные значения строки и столбца, то данные по сигналу WE# (Write Enabled) записываются из буфера ввода/вывода в конкретную ячейку памяти, либо считываются из нее в буфер (WE# = 1 – считывание; WE# = 0 – запись). Интервал времени между началом обращения к памяти и получением (записью) данных, называется временем обращения (tобр.) к памяти и определяет ее быстродействие.

3 Асинхронная динамическая память

Изначально процесс доступа к памяти шел «сам по себе», без какой-либо «привязки» к работе остальной компьютерной системы. Такой режим работы получил название асинхронного режима, а память называли – асинхронной динамической памятью. Механизм работы асинхронной динамической памяти был довольно простым, но количество задержек в ее работе было очень велико – невозможно было точно сказать, когда система будет работать, а когда будет свободна. В персональных компьютерах использовалось несколько типов асинхронной динамической памяти.

Память FRM (Fast Page Mode) использовалась на системах типа XT, 286, 386, 486, начальных моделях Pentium. Время минимального доступа памяти FRM составляло 60 нс.

Память EDO (Extended Date Out) – был предложен другой алгоритм управления выдачей данных на шину, но ускорение достигалось только в режиме считывания информации.

Память BEDO (Burst EDO) – разработка фирмы VIA, была применена в некоторых чипсетах этой фирмы и широкого распространения не получила.

4 Синхронная динамическая память

Быстродействие асинхронной памяти довольно быстро себя исчерпало – частоты 70..75 МГц стали для нее пределом. На смену асинхронному режиму пришел новый принцип организации работы памяти, получивший название синхронного режима.

Основные возможности синхронной динамической памяти:

- продолжительность всех временных интервалов строго фиксирована;

- все действия производятся по истечении определенных временных интервалов;

- модуль памяти содержит внутренний блок генерации частоты, работающий на системной частоте или значениях, кратных ей;

- продолжительность всех временных интервалов измеряется в тактах частоты шины памяти; этим занимаются специальные счетчики контроллера памяти;

- работа памяти ведется по обоим фронтам синхросигнала (положительному и отрицательному), т.е., через полтакта;

- возможна пакетная передача данных; организация очереди запросов на доступ к матрице; поддерживается несколько режимов регенерации;

- организовано два независимых физических массива, состоящих из 4 логических банков каждый. Возможно параллельное обращение к двум логическим банкам разных логических массивов, что значительно повышает производительность работы синхронной динамической памяти.

Контрольные вопросы:

1 Как на физическом уровне организована ячейка статической памяти? Какие преимущества имеет этот вид памяти по отношению к динамической памяти?

2 Как на физическом уровне организована ячейка динамической памяти? Какие преимущества имеет этот вид памяти по отношению к статической памяти?

3 Какие характеристики динамической памяти обосновали выбор такой памяти для организации ОЗУ?

4 Что характерно для работы асинхронной динамической памяти?

5 Какие новые возможности были реализованы в синхронной динамической памяти?

Домашнее задание.

1 Законспектировать материал по теме в тетради.

2 Ответить на контрольные вопросы

Литература

1 Д. Паттерсон, Дж. Хеннесси Архитектура компьютера и проектирование компьютерных систем. Классика Computers Science. 4-е изд.– СПб.: Питер, 2017. – 784 с.: ил.

2 Таненбаум Э., Остин Т. Архитектура компьютера. 6-е изд. – СПб.: Питер, 2018. – 816 с.: ил.

3 Жмакин А.П. Архитектура ЭВМ. – СПб.: БХВ – Петербург, 320с. /2018

4 Скачано с www.znanio.ru

Материалы на данной страницы взяты из открытых источников либо размещены пользователем в соответствии с договором-офертой сайта. Вы можете сообщить о нарушении.