Практическое занятие № 18

Тема: «Изображение комбинационных устройств в микросхемах - шифраторы»

Цель: изучить различные микросхемы, выполняющие роль шифраторов, спроектировать схемы на двух и более шифраторах

Теория

Шифратор — это комбинационное устройство, преобразующее десятичные числа в двоичную систему счисления, причем каждому входу может быть поставлено в соответствие десятичное число, а набор выходных логических сигналов соответствует определенному двоичному коду. Шифратор иногда называют «кодером» (от англ. coder) и используют, например, для перевода десятичных чисел, набранных на клавиатуре кнопочного пульта управления, в двоичные числа.

Таким образом, шифратор (кодер), это электронное устройство, в данном случае микросхема, которая преобразует код одной системы счисления в код другой системы. Наибольшее распространение в электронике получили шифраторы, преобразующие позиционный десятичный код, в параллельный двоичный.

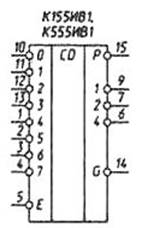

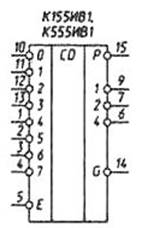

Они имеют обозначение на схемах буквами CD, а в названии микросхем имеют суффикс ИВ. Обычно имеют от 4 до 16 (чаще всего 8) информационных входов, от 2 до 4 выходов (чаще всего 3) и несколько стробирующих (разрешающих) входов и выходов. Типичными представителями данных типов микросхем являются микросхемы К555ИВ1, К155ИВ1 и К555ИВ3.

Рассмотрим приоритетный шифратор с выходом переноса и входом разрешения шифрации.

Микросхема К155 (К555) ИВ1 имеет восемь входов для подачи десятичного кода 1-7 (активный уровень низкий) и три выхода для вывода двоичного кода входного сигнала (активный уровень также низкий). При отсутствии входного кода (все уровни на выводах 1-4 и 10-13 высокие) на выводах 9, 7, 6 устанавливается высокий уровень, при появлении на любом из входов низкого уровня, на выходе устанавливается соответствующий номеру входа двоичный трехразрядный код. Одновременно на выходе G появляется «0» (сигнал наличия входного кода) и «1» на выходе Р, который используется для запрещения работы остальных шифраторов при их каскадном включении.

Если низкий уровень появляется одновременно на нескольких входах, то обрабатывается старший разряд, все младшие игнорируются. Такой режим обеспечивается внутренней схемой приоритета. Для наращивания разрядности кроме сигнала «перенос» (вывод 15) используется вход разрешения шифрации (вывод 5). При появлении на нем высокого уровня работа микросхемы запрещена и на ее выходах устанавливаются высокие уровни.

Ход работы

Спроектировать схему приоритетного шифратора на 16 входов и 4 выхода, используя две микросхемы на 8 входов и 4 выхода. Выполнить эскиз в тетради и начертить схему на формате А4.

Практическое занятие № 18

Тема: «Изображение комбинационных устройств в микросхемах - шифраторы»

Цель: изучить различные микросхемы, выполняющие роль шифраторов, спроектировать схемы на двух и более шифраторах

Теория

Шифратор — это комбинационное устройство, преобразующее десятичные числа в двоичную систему счисления, причем каждому входу может быть поставлено в соответствие десятичное число, а набор выходных логических сигналов соответствует определенному двоичному коду. Шифратор иногда называют «кодером» (от англ. coder) и используют, например, для перевода десятичных чисел, набранных на клавиатуре кнопочного пульта управления, в двоичные числа.

Таким образом, шифратор (кодер), это электронное устройство, в данном случае микросхема, которая преобразует код одной системы счисления в код другой системы. Наибольшее распространение в электронике получили шифраторы, преобразующие позиционный десятичный код, в параллельный двоичный.

Они имеют обозначение на схемах буквами CD, а в названии микросхем имеют суффикс ИВ. Обычно имеют от 4 до 16 (чаще всего 8) информационных входов, от 2 до 4 выходов (чаще всего 3) и несколько стробирующих (разрешающих) входов и выходов. Типичными представителями данных типов микросхем являются микросхемы К555ИВ1, К155ИВ1 и К555ИВ3.

Рассмотрим приоритетный шифратор с выходом переноса и входом разрешения шифрации.

Микросхема К155 (К555) ИВ1 имеет восемь входов для подачи десятичного кода 1-7 (активный уровень низкий) и три выхода для вывода двоичного кода входного сигнала (активный уровень также низкий). При отсутствии входного кода (все уровни на выводах 1-4 и 10-13 высокие) на выводах 9, 7, 6 устанавливается высокий уровень, при появлении на любом из входов низкого уровня, на выходе устанавливается соответствующий номеру входа двоичный трехразрядный код. Одновременно на выходе G появляется «0» (сигнал наличия входного кода) и «1» на выходе Р, который используется для запрещения работы остальных шифраторов при их каскадном включении.

Если низкий уровень появляется одновременно на нескольких входах, то обрабатывается старший разряд, все младшие игнорируются. Такой режим обеспечивается внутренней схемой приоритета. Для наращивания разрядности кроме сигнала «перенос» (вывод 15) используется вход разрешения шифрации (вывод 5). При появлении на нем высокого уровня работа микросхемы запрещена и на ее выходах устанавливаются высокие уровни.

Ход работы

Спроектировать схему приоритетного шифратора на 16 входов и 4 выхода, используя две микросхемы на 8 входов и 4 выхода. Выполнить эскиз в тетради и начертить схему на формате А4.

Материалы на данной страницы взяты из открытых источников либо размещены пользователем в соответствии с договором-офертой сайта. Вы можете сообщить о нарушении.