Если при передачи данных между регистрами и функциональными устройствами выполняются по тактовым сигналам, то при повышении тактовой частоты уменьшается время получения результатов. Такая организация вычислений называется аппаратной, или схемной. При схемной реализации вычислений все управляющие сигналы мультиплексоров фиксированы, т.е. на соответствующие управляющие входы поданы либо заданные совокупности постоянных значений, либо выходы определенных блоков схемы.

Схемная реализация демонстрирует два способа, применяемых для минимизации времени вычислений: параллельность и конвейерность обработки.

Параллельность заключается в одновременном выполнении преобразований в нескольких функциональных устройствах.

Конвейерность служит частным случаем параллельности, при котором выполнение преобразований, необходимых для получения каждого результата из однородной совокупности результатов. Для выполнения каждого шага алгоритма используются отдельные устройства, совокупность преобразований в которых составляет весь алгоритм требуемого преобразования. Результат каждого устройства, входящего в конвейер, фиксируется в регистре, и следующее устройство использует этот предварительно сохраненный результат, что позволяет совместить во времени выполнения очередного шага.

Достоинством конвейерной реализации служит то, что после того, как все устройства конвейера загружены работой, очередной результат преобразования выдается на выходе через промежуток времени, равный длительности одного шага. И это при том, что время получения этого результата равно суммарной длительности всех шагов конвейера.

Схемная реализация вычислений требует создания уникальной схемы объединения регистров и функциональных устройств, соответствующей заданному алгоритму. Поэтому переход от реализации одного алгоритма к реализации другого фактически требует построения новой вычислительной установки. Это очень трудоемкий процесс.

Для обеспечения возможности выполнения разных алгоритмов при одной и той же схеме объединения регистров и функциональных устройств применяют программную реализацию вычислений.

При программной реализации вычислений изначально устанавливается набор регистров, функциональных устройств и мультиплексоров, через которые возможны передачи данными между ними. Задается также набор команд, служащий для записи алгоритма требуемого вычисления. Каждая команда, будучи исполняемой, вырабатывает совокупность управляющих сигналов, подаваемых на некоторые мультиплексоры, что ведет к межрегистровым передачам данных с возможным преобразованием данных в функциональных устройствах.

Таким образом, при программной реализации вычислений за счет возможности исполнения различных последовательностей команд возможно при одной и той же схеме соединения регистров, мультиплексоров и функциональных устройств реализовать различные алгоритмы.

Программная реализация вычислений требует подачи определенной последовательности команд для выполнения необходимого вычисления.

Понятие «процессор» появилось как результат творческого озарения группы инженеров, работавших под техническим руководством Дж. Мочли и Дж. Эккерта над созданием ENIAC (Electronic Numerical Integrator and Computer – электронного цифрового интегратора и вычислителя), при проектировании совместно с математиком Дж. Фон Нейманом компьютера ENIAC. пришедшая им в головы идея состояла в том, что команды, исполнение совокупности которых необходимо для реализации вычисления, можно так же как данные хранить в памяти, а для их выполнения создать схемную реализацию алгоритма, обеспечивающего требуемый порядок исполнения команд. Этот схемно реализованный алгоритм и был впоследствии назван процессор.

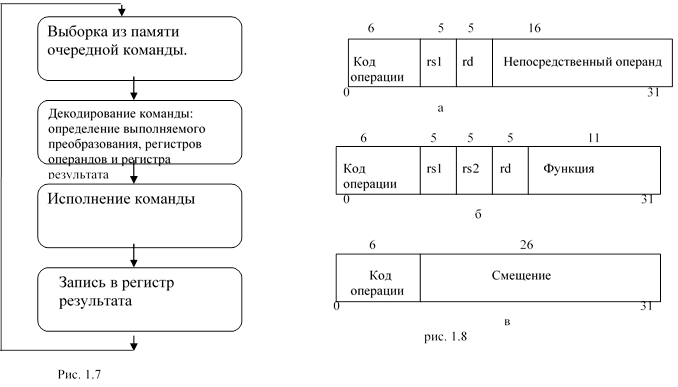

Суть этого алгоритма сводится к циклическому исполнению следующих шагов (рис. 1.7).

В качестве примера рассмотрим некоторый модельный процессор DLX. Набор команд процессора DLX состоит из команд трех типов:

o чтения/записи;

o преобразований в арифметико-логическим устройстве (АЛУ);

o переходов.

Форматы этих типов команд представлены на рис 1.8 а, б, в соответственно.

Команды чтения/записи в зависимости от значения, содержащегося в 6-битном поле «код операции», выполняют следующие действия:

· пересылают данные из регистра источника rs1 в регистр результата rd;

· пересылают 16-битную константу, содержащуюся в поле «непосредственный операнд», в регистр rd;

· пересылают данные из регистра в память и из памяти в регистр.

Скачано с www.znanio.ru

Материалы на данной страницы взяты из открытых источников либо размещены пользователем в соответствии с договором-офертой сайта. Вы можете сообщить о нарушении.