Практическое занятие № 83

Тема: «Проектирование и построение цифровых устройств (сумматоров) с использованием компонентов программного пакета Microsoft Visio»

Цель: овладение навыками проектирования схем различной сложности с использованием программного пакета Microsoft Visio.

1. В тетради записать Дату, Тему, Цель. В ходе работе дать определение проектируемого цифрового устройства, составить таблицу истинности его работы, для каждого выхода написать логическое выражение.

2. Используя полученное выражение, спроектировать схему вручную на листе формата А4. Основную надпись выполнить от руки.

3. Задания выполнять в печатном виде в программе Microsoft Visio.

Номера заданий 13-16.

ЗАДАНИЯ

1. Спроектировать схему дешифратора двоичного кода в десятичный с использованием базовых логических элементов на 10 выходов. Определить полный или не полный дешифратор.

2. Спроектировать схему дешифратора двоичного кода в десятичный с использованием базовых логических элементов на 12 выходов. Определить полный или не полный дешифратор.

3. Спроектировать схему дешифратора двоичного кода в десятичный с использованием базовых логических элементов на 14 выходов. Определить полный или не полный дешифратор.

4. Спроектировать схему дешифратора двоичного кода в десятичный с использованием базовых логических элементов на 16 выходов. Определить полный или не полный дешифратор.

5. Спроектировать схему дешифратора двоичного кода в десятичный с использованием базовых логических элементов на 4 входа. Определить полный или не полный дешифратор.

6. Спроектировать схему дешифратора двоичного кода в десятичный с использованием базовых логических элементов на 5 входов. Определить полный или не полный дешифратор.

7. Спроектировать схему дешифратора двоичного кода в десятичный с использованием базовых логических элементов на 3 входа. Определить полный или не полный дешифратор.

8. Спроектировать схему дешифратора двоичного кода в десятичный с использованием базовых логических элементов на 6 входа. Определить полный или не полный дешифратор.

9. Спроектировать схему мультиплексора с использованием базовых логических элементов на 8 входов.

10. Спроектировать схему мультиплексора с использованием базовых логических элементов на 8 входов

11. Спроектировать схему мультиплексора с использованием базовых логических элементов на 6 входов

12. Спроектировать схему мультиплексора с использованием базовых логических элементов на 10 входов

13. Спроектировать схему трехразрядного сумматора с последовательным переносом с использованием полусумматоров.

14. Спроектировать схему трехразрядного сумматора с параллельным переносом с использованием полусумматоров.

15. Спроектировать схему четырёхразрядного сумматора с параллельным переносом с использованием полусумматоров.

16. Спроектировать схему четырёхрядного сумматора с последовательным переносом с использованием полусумматоров.

17. Спроектировать схему цифрового шифратора десятичного кода в двоичный с использованием базовых логических элементов на 10 входов

18. Спроектировать схему цифрового шифратора десятичного кода в двоичный с использованием базовых логических элементов на 12 входов

19. Спроектировать схему цифрового шифратора на логических элементах И-НЕ на 10 входов.

20. Спроектировать схему цифрового шифратора десятичного кода в двоичный с использованием базовых логических элементов на 14 входов

21. Спроектировать схему цифрового шифратора десятичного кода в двоичный с использованием базовых логических элементов на 8 входов.

22. Спроектировать схему цифрового шифратора десятичного кода в двоичный с использованием базовых логических элементов на 16 входов

23. Спроектировать схему цифрового шифратора на логических элементах И-НЕ на 11 входов

24. Спроектировать схему цифрового шифратора на логических элементах И-НЕ на 13 входов

25. Спроектировать схему цифрового шифратора на логических элементах И-НЕ на 15 входов

ПРИМЕР ВЫПОЛНЕНИЯ ЗАДАНИЯ

Практическое занятие № 83

Тема: «Проектирование и построение цифровых устройств (сумматоров) с использованием компонентов программного пакета Microsoft Visio»

Цель: овладение навыками проектирования схем различной сложности с использованием программного пакета Microsoft Visio.

Ход работы

1. Дать определение цифрового устройства, составить таблицу истинности его работы, для каждого выхода написать логическое выражение и с помощью программного комплекса Microsoft Visio создать схему однорядного полного сумматора с параллельным переносом с использованием полусумматоров.

ОТВЕТ

Сумматор — это устройство, предназначенное для сложения двоичных чисел.

Рассмотрим сначала более простое устройство – полусумматор.

Построим таблицу истинности для устройства реализующего арифметическую операцию сложения. Операция «+» бинарная, поэтому полусумматор должен иметь два входа (A и B). В результате сложения двух одноразрядных двоичных чисел может получиться двухразрядное число (с переносом в следующий разряд). Значит, устройство должно иметь два выхода (P - перенос в следующий разряд, S - результат, остающийся в текущем разряде).

|

А |

B |

P |

S |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

0 |

По данной таблице истинности построим логические выражения

1. Для переноса в старший разряд: P = A • B

2. Для текущего разряда: S = ¬ A • B + A • ¬ B

Преобразуем логическую формулу для

S:

(¬ A • B) + (A • ¬ B) = (¬ A • A) + ( ¬ A • B) (A • ¬ B) + (¬ B • B) =

= ¬ A • (A + B) + ¬ B • (A + B) = (A + B) • ¬ (A • B)

С учетом формулы для переноса имеем:

S = (A + B) • ¬ (A • B) = (A + B) • ¬ P

Таким образом, полусумматор можно построить, используя четыре простейших логических элемента: два конъюнктора, дизъюнктор и инвертор

Итак, получено устройство, реализующее суммирование одноразрядных двоичных чисел без учета переноса из младшего разряда.

Для реализации полного одноразрядного сумматора необходимо учесть перенос из младшего разряда (P0). Поэтому сумматор должен иметь три входа. Построим таблицу истинности для устройства с учетом третьего входа:

|

А |

B |

P0 |

P |

S |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

1 |

|

0 |

1 |

0 |

0 |

1 |

|

0 |

1 |

1 |

1 |

0 |

|

1 |

0 |

0 |

0 |

1 |

|

1 |

0 |

1 |

1 |

0 |

|

1 |

1 |

0 |

1 |

0 |

|

1 |

1 |

1 |

1 |

1 |

Построим логические выражения для выхода P (перенос в старший разряд): P = (¬ A ∧ B ∧ P0) ∨ (A ∧ ¬ B ∧ P0) ∨ (A ∧ B ∧ ¬ P0) ∨ (A ∧ B ∧ P0)

Преобразуем:

1) (A ∧

B ∧

¬ P0) ∨ (A ∧

B ∧

P0) = (A ∧ B) ∧

(¬ P0 ∨ P0) = A ∧

B

Имеем,

P

= (¬ A ∧ B

∧ P0)

∨

(A ∧

¬ B ∧ P0)

∨

(A ∧ B)

2) (¬ A ∧ B

∧ P0)

∨

(A ∧ B)

= B ∧(¬

A ∧ P0 ∨ A)

= B ∧

(¬ A ∨ A

) ∧

(P0 ∨ A)

=

= B ∧

(P0 ∨ A)

= (B ∧ P0)

∨

(A ∧ B)

Имеем,

P

= (A ∧

¬ B ∧ P0)

∨

(B ∧ P0)

∨

(A ∧ B)

3) (A ∧ B)

∨

(A ∧

¬ B ∧ P0)

= A ∧

(B ∨

¬ B ∧ P0)

= A ∧

(B ∨

¬ B)(B

∨ P0)

=

= A ∧

(B ∨ P0)

= (A ∧ B)

∨

(A ∧ P0)

Таким образом, для переноса в старший разряд получили: P = A ∧ B ∨ A ∧ P0 ∨ B ∧ P0

Проанализируем таблицу истинности для выхода S. Значение S отлично от нуля в том случае, если единица поступает ровно на один вход (при этом на двух других входах фиксируется ноль), или на все три входа сразу, т. е.:

S = ¬ (A ∧ B ∨ A ∧ P0 ∨ B ∧ P0) ∧ (A ∨ B ∨ P0) ∨ (A ∧ B ∧ P0)

С учетом формулы для переноса в старший разряд, имеем:

S = ¬ P ∧ (A ∨ B ∨ P0) ∨ (A ∧ B ∧ P0)

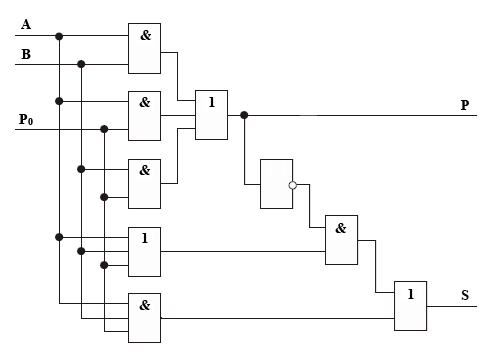

Таким образом, одноразрядный двоичный сумматор можно реализовать с помощью следующей схемы, которая соответствует полученным логическим формулам.

Материалы на данной страницы взяты из открытых источников либо размещены пользователем в соответствии с договором-офертой сайта. Вы можете сообщить о нарушении.