Практическое занятие № 3

Тема: «Изучение программного обеспечения микропроцессорных систем»

Цель: изучение микропроцессорной секции 1804ВС1, принципов микропрограммирования режимов ее работы и взаимодействия ее с блоком микропрограммного управления (микропроцессорной секцией 1804ВУ1).

Ход работы

Перед выполнением работы следует ознакомиться с следующими теоритическими данными:

- изучить структурную схему микропроцессорной секции К1804ВС1, основные блоки и взаимодействие между ними;

- знать управляющие входы БИС и задаваемые с их помощью функции, порядок взаимодействия блоков;

- изучить основные системные параметры БИС;

Теория

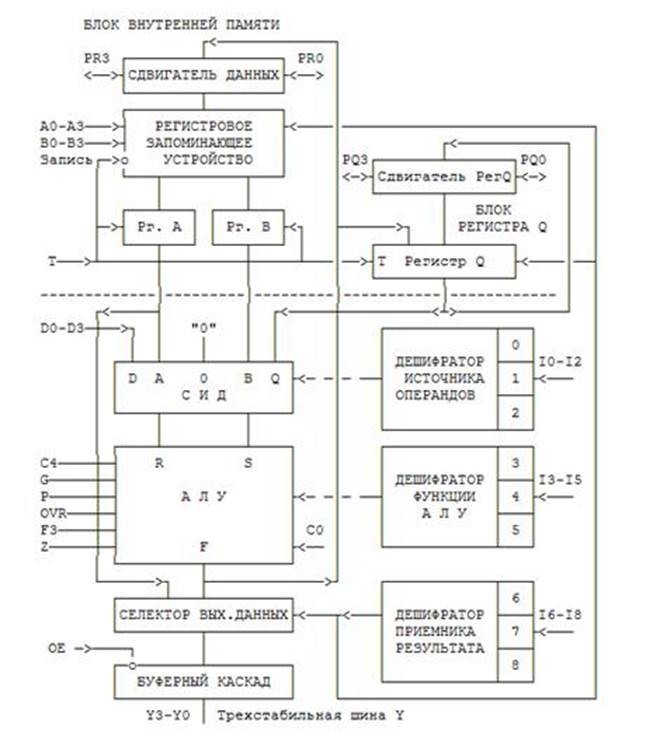

На рисунке 2.1 приведена четырехразрядная микропроцессорная секция 1804ВС1, предназначенная для построения операционных блоков цифровых устройств с разрядностью, кратной четырем.

На схеме можно выделить следующие четыре крупных блока:

- блок внутренней памяти;

- блок арифметико-логический;

- блок регистра Q;

- блок управления;

Блок внутренней памяти:

- Регистровое запоминающее устройство РЗУ с двумя независимыми каналами выбора информации по адресам A и B;

- На входе РЗУ (регистрового запоминающего устройтсва) включен сдвигатель данных СДА, позволяющий записывать данные в РЗУ как без сдвига, так и со сдвигом влево или вправо на один разряд;

- Запись в РЗУ возможна только по адресу B;

- Регистры РгA и РгB на выходе РЗУ представляют собой 4-разрядные параллельные регистры с однофазной записью;

- Выбор из блока внутренней памяти любого регистра общего назначения (РОН) в качестве источника инофрмации осуществляется сигналами на адресных входах A0 – A3 или B0 – B3. Запись данных адресуется в РОН, адресуемый сигналами на адресных входам B0 – B3.

Рисунок 2.1 – схема четырехразрядной микропроцессорной секции 1804ВС1

- Как уже говорилось, информация может быть сдвинута на разряд влево или вправо с помощью СДА, управляемый сиганалами с дешифратора приёмника результата.

Арифметически-логический блок:

- Включает в себя двухвходовое АЛУ, выполняющее 8 операций и формирующее четыре признака результата (перенос из старшего разряда C4, переполнение OVR, знак или содержимое старшего разряда на выходе F3 АЛУ, признак Z – нулевое значение результата на всех выходах АЛУ).

- На выходах АЛУ включен селектор источника данных (СИД), позволяющий комбинировать в качестве пары операндов АЛУ информацию из пяти источников: с внешней шины данных D0-D3, с каналов A и B, с регистра Q. Пятый источник – условный, он представляет собой нулевую константу, которую можно подать на один из входов АЛУ.

- С выхода АЛУ информация подается на селектор выходных данных (СВД). На второй вход селектора инофрмация может быть передана прямо с выхода А РЗУ, минуя АЛУ.

- С выхода СВД информация через управляемые усилители передается на выходную шину МПС, трехстабильную шину Y.

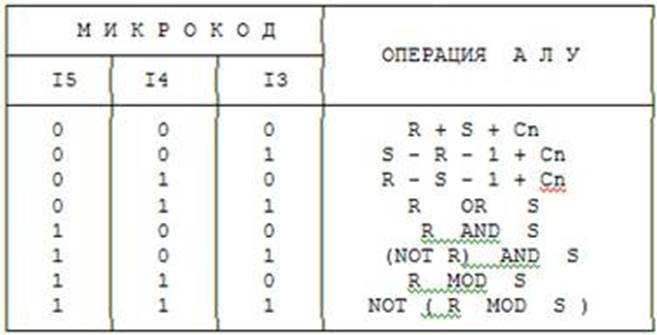

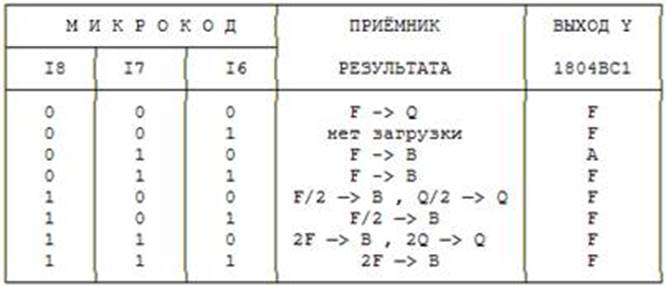

- Управление арифметическо-логическим блоком осуществляется в соответствии с таблицами 2.1 – 2.3:

Таблица 2.1 – управление источниками операндов:

Таблица 2.2 – зависимость функции АЛУ от кода микрокоманды:

OR – логическое ИЛИ; AND – логическое И; NOT – инверсия; MOD – сложение по модулю 2.

Таблица 2.3 – управление приёмником результата:

F3, OVR, C4 – флаги состояния АЛУ;

F – результат опреации АЛУ;

Арифметические операции в АЛУ выполняются с учетом значения сигнала входного переноса C0, по правилам дополнительного кода при представлении чисел.

Блок управления:

- Формирует управляющие сигналы для остальных блоков МПС. Входами блока являются шины кода микрокоманды I0-I8, которые, согласно формату микрокоманды, можно разделить на три группы. Блок управления также можно представить состоящим из трёх частей, причем первая вырабатывает сигналы управления для СИД, вторая - для АЛУ, а третья - для СВД, РгQ и сдвигателей СДР и СДА. Вырабатываемые микропроцессорной секцией 1804ВС1 признаки фиксируются в регистре состояния и через мультиплексор передаются на вход схемы 1804ВУ1 для осуществления способов адресации по условиям ( нулевой результат, перенос и т. д.).

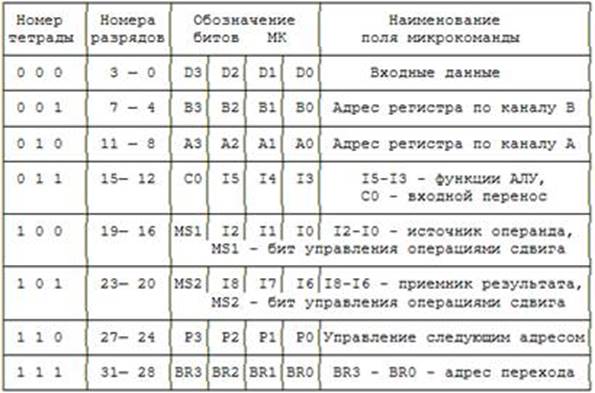

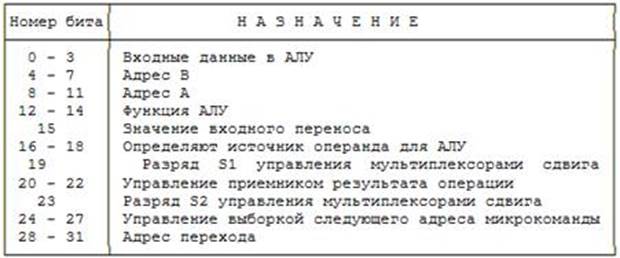

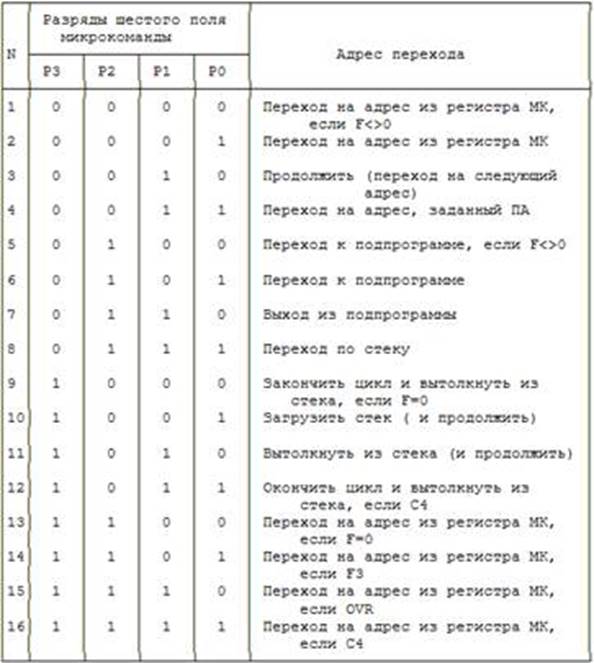

На рисунке 2.2 – 2.4 показаны формат, значения битов, зависимость адреса перехода от кода микрокоманды операционного блока 1804ВС1:

Рисунок 2.2 – формат микрокоманды операционного блока 1804ВС1

Рисунок 2.3 – значения битов микрокоманды операционного блока 1804ВС1

Рисунок 2.4 – зависимость адреса перехода от кода микрокоманды операционного блока 1804ВС1

В МТ1804 имеется три группы переключателей: переключатели "АДДРЕС", переключатели "ДАННЫЕ" и переключатели "МУЛЬТИПЛЕКСОР", которые обеспечивают занесение в микропрограммную память исследуемые программы. Кроме того устройство содержит :

- переключатель режимов "ЗАГРУЗКА/РАБОТА";

- кнопку ЗАГРУЗКА;

- кнопку ПУСК.

Светодиодные индикаторы "МИКРОКОМАНДА" предназначены для индикации содержимого регистра микрокоманд. Индикация 32-разрядного слова четырьмя светодиодами осуществляется потетрадно.

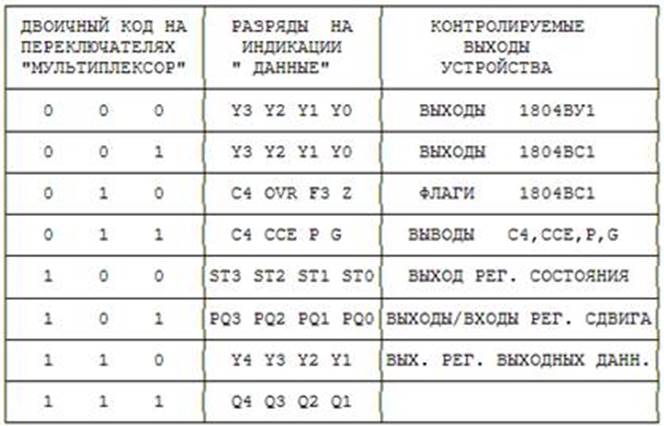

Номер тетрады, выводимой на индикацию, определяется положением переключателей "МУЛЬТИПЛЕКСОР" в двоичном коде. ВЕРХНЕЕ ПОЛОЖЕНИЕ ПЕРЕКЛЮЧАТЕЛЯ СООТВЕТСТВУЕТ ЛОГИЧЕСКОЙ ЕДИНИЦЕ.

Светодиодные индикаторы "ПАМЯТЬ" предназначены для индикации содержимого микропрограммной памяти. Содержимое нужного адреса памяти выводится на индикацию потетрадно в соответствии с положением переключателей "ДАННЫЕ" и "МУЛЬТИПЛЕКСОР", причем двоичный код, набранный на переключателях "МУЛЬТИПЛЕКСОР" соответствует номеру тетрады.

Светодиодные индикаторы "ДАННЫЕ" предназначены для индикации прохождения данных в тридцати двух точках схемы устройства. Коммутация светодиодов осуществляется переключателями

" МУЛЬТИПЛЕКСОР ".

На рисунке 2.5 показаны отображаемые на индикаторы выходы операционного блока 1804ВС1;

Материалы на данной страницы взяты из открытых источников либо размещены пользователем в соответствии с договором-офертой сайта. Вы можете сообщить о нарушении.