Практическое занятие № 22

Тема: «Структура ЗУ. Основные блоки ЗУ. Изучение подсистемы оперативной памяти ПК с КЭШем»

Цель: изучить структуру оперативной памяти и её кэш-памяти, рассмотреть назначение и общие принципы построения кэш-памяти микропроцессора, а также особенности ее использования в микропроцессорных системах.

Теория

Кроме центрального процессора и микропроцессорного комплекта (чипсета) на материнской плате расположено еще одно важнейшее устройство - оперативная память или оперативное запоминающее устройство (RAM – Random Access Memory) или ОЗУ.

Очень важным элементом компьютера является оперативная память. Именно из нее процессор берет программы и исходные данные для обработки, в нее он записывает полученные результаты. Название «оперативная» эта память получила потому, что она работает очень быстро, так что процессору практически не приходится ждать при чтении данных из памяти или записи в память. Однако содержащиеся в ней данные сохраняются только пока компьютер включен. При выключении компьютера содержимое оперативной памяти стирается.

От количества установленной в компьютере оперативной памяти напрямую зависит, с какими программами Вы сможете на нем работать. При недостаточном количестве оперативной памяти многие программы либо вовсе не будут работать, либо станут работать крайне медленно.

Эта память используется для временного хранения данных, обрабатываемых центральным процессором. Однако в ОЗУ хранятся не только данные, туда перед запуском должна быть записана программа.

Существует много различных типов ОП, но с точки зрения физического принципа действия различают динамическую память (DRAM) и статическую память (SRAM).

Ячейки с динамической памяти (DRAM) можно представить в виде микро конденсаторов, способных накапливать заряд на своих обкладках. Это наиболее распространенный и экономически доступный тип памяти. Недостатки этого типа связаны, во-первых, с тем, что как при заряде, так и при разряде конденсаторов неизбежны переходные процессы, то есть запись данных происходит сравнительно медленно. Второй недостаток связан с тем, что заряды ячеек имеют свойство рассеиваться в пространстве. Если ОП постоянно не «подзаряжать», утрата информации происходит мгновенно. Для устранения этого в компьютере происходит постоянная регенерация (подзарядка) ячеек оперативной памяти. Регенерация осуществляется несколько раз в секунду и вызывает непроизводительный расход ресурсов вычислительной системы.

Ячейки статической памяти (SRAM) можно представить, как электронные микроэлементы – триггеры, состоящие из нескольких транзисторов. В триггерах хранится не заряд, а состояние, поэтому этот тип памяти обеспечивает более высокое быстродействие, хотя технологически он сложен и, соответственно, дороже.

Память ЭВМ организована по иерархической лестнице, т.е. устройства, обладающие большим объемом памяти обладают меньшим быстродействием. Наибольшим быстродействием обладают СОЗУ (сверх ОЗУ). Они обычно реализуются на регистрах, поэтому в МП СОЗУ называется РОН. Объем памяти СОЗУ очень мал. Обычно памятью машины называют ОЗУ. Быстродействие ОЗУ должно быть не меньше чем быстродействие электронных схем операционной части, памяти должно быть достаточно для записи программы решаемой задачи, а также исходных данных, промежуточных и конечных результатов. Внешние запоминающие устройства обладают практически неограниченным объемом памяти и наименьшим быстродействием. ОЗУ не сохраняет информацию при отключении питания. Существуют ПЗУ, которые сохраняют информацию при отключении питания. ПЗУ работают только в режиме чтения, а ОЗУ в режиме чтения и записи. Существуют перепрограммируемые ПЗУ (ППЗУ), которые сохраняют информацию при отключении питания и допускают запись информации. При этом время записи во много раз больше времени считывания. Считывание информации из ОЗУ может происходить с разрушением информации или без.

При разрушении информации при считывании необходимо дополнительное время на восстановление информации. Время считывания состоит из времени поиска адреса, времени собственного считывания и времени регенерации (восстановления) считанной информации. ОЗУ реализуется на микросхемах. Элемент памяти реализован на триггерах. Триггер может быть построен на биполярных и униполярных транзисторах.

По шине адреса (ША) в регистр адреса поступает n - разрядный двоичный код адреса. n1 разряд используется для записи номера строки, а n2 - для записи номера столбца. Дешифраторы строк и столбцов вырабатывают управляющие сигналы на соответствующих выходах. Под действием этих управляющих сигналов происходит выбор адресуемого элемента памяти, если на входе выбора кристалла (ВК) дешифратора строк "1", то ОЗУ находится в режиме хранения. Если на ВК "0", то ОЗУ находится или в режиме чтения, или в режиме записи. Нормальным является режим чтения.

Информация поступает через усилитель чтения (УЧ) и выходной триггер.

|

|

Рисунок 1.

Режим записи обеспечивается подачей сигнала разрешения записи (РЗ) на усилитель записи (УЗ). Информация через триггер и УЗ подается на информационные цепи 1 и 0. Триггеры реализованы на МДП - транзисторах.

Транзисторы VT2 и VT4 являются нагрузкой триггера. Напряжение затвор - исток этих транзисторов имеет нулевое значение, поэтому они всегда открыты. Триггер реализован на VT1 и VT3. В нем записана "1", если VT1 закрыт. При совпадении сигналов от дешифратора строк и столбцов триггер готов к записи или считыванию информации. Управляющий сигнал с выхода дешифратора столбцов действует на VT7 и VT8. Управляющий сигнал с выхода дешифратора строк воздействует на VT5 и VT6.

Запись "1" производится в том случае, если на информационную цепь (ИЦ) нуля поступает логический "0". Для записи "0" логический "0" подается в ИЦ1.

В режиме чтения состояние триггера передается через открытые VT5-VT8 в информационные цепи. Если элемент памяти хранит "1", то уровень "1" поступает в ИЦ1, а если "0", то уровень логической "1" поступает в ИЦ0.

Кэш- память. Для достаточно быстрых компьютеров (например, на основе Intel® Pentium® 4 / Celeron с тактовой частотой от 1.4 до 3.06ГГц и выше) необходимо обеспечить быстрый доступ к оперативной памяти, иначе микропроцессор будет простаивать и быстродействие компьютера уменьшится. Для этого такие компьютеры могут оснащаться кэш-памятью, т.е. "сверхоперативной" памятью относительно небольшого объема (обычно от 64 до 256 Кбайт), в которой хранятся наиболее часто используемые участки оперативной памяти.

Кэш-память располагается "между" микропроцессором и оперативной памятью, и при обращении микропроцессора к памяти сначала производится поиск нужных данных в кэш-памяти. Поскольку время доступа к кэш-памяти в несколько раз меньше, чем к обычной памяти, а в большинстве случаев необходимые микропроцессору данные содержаться в кэш-памяти, среднее время доступа к памяти уменьшается. Для компьютеров на основе Intel-80386DX или 80486SX размер кэш-памяти в 64 Кбайт является удовлетворительным,128 Кбайт - вполне достаточным. Компьютеры на основе Intel-80486DX и DX2 обычно оснащаются кэш-памятью емкостью 256 Кбайт.

Каждая ячейка памяти имеет свой адрес, который выражается числом. В настоящее время в процессорах Intel Pentium и некоторых других принята 32-разрядная адресация, а это означает, что всего независимых адресов может быть 232. Предельный размер поля оперативной памяти, установленной в компьютере, определяется микропроцессорным комплектом (чипсетом) материнской платы и обычно составляет несколько сот Мбайт.

Конструктивно модули памяти имеют два исполнения – однорядные (SIMM –модули) и двухразрядные (DIMM – модули). На компьютерах с процессорами Pentium однорядные модули можно применять только парами (количество разъемов для их установки на материнской плате всегда четное), а DIMM – модули можно устанавливать по одному.

Основными характеристиками модулей ОП являются объем памяти и время доступа. SIMM –модули поставляются объемами 4,8,16,32 Мбайт, а DIMM – модули – 16,32,64,128 Мбайт и более. Время доступа показывает, сколько времени необходимо для обращения к ячейкам памяти – чем оно меньше, тем лучше. Время доступа к ОП для SIMM – модулей – 50 – 70 нс. Для DIMM – модулей оно составляет 7-10 нс.

Почему вся память компьютера не работает так же быстро, как ОЗУ? Тому есть две причины. Во-первых, быстродействующая память дорого стоит. Во-вторых, все данные, хранящиеся в ОЗУ, пропадают при выключении питания компьютера.

Кроме ОЗУ на материнской плате есть микросхема постоянного запоминающего устройства (ROM или ПЗУ). Данные записываются в ПЗУ один раз при изготовлении микросхемы на заводе и обычно не могут быть изменены впоследствии. В ПЗУ хранятся программы, которые компьютер запускает автоматически при включении питания.

В момент включения компьютера процессору нужны команды. Поэтому сразу после включения на адресной шине процессора выставляется стартовый адрес. Это происходит аппаратно, без участия программ. Процессор обращается по выставленному адресу за свой первой командой. Этот исходный адрес не может указывать на оперативную память, в которой ничего нет. Он указывает на другой тип памяти – постоянное запоминающее устройство (ПЗУ). Далее начинает работать по программам.

Эти программы предназначены для проверки исправности и обслуживания аппаратуры самого компьютера. Они также выполняют первоначальную загрузку главной обслуживающей программы компьютера - так называемой операционной системы.

Микросхема ПЗУ способна длительное время хранить информацию, даже когда компьютер выключен.

Комплект программ, находящихся в ПЗУ, образует базовую систему ввода-вывода (BIOS – Basic Input Output System). Основные назначение программ этого пакета состоит в том, чтобы проверить состав и работоспособность компьютерной системы и обеспечить взаимодействие с клавиатурой, монитором, жестким диском и дисководом гибких дисков.

Внутренний кэш 32-разрядного универсального микропроцессора является общим при обращении как к командам, так и к данным. Обращение ведется по физическим адресам.

Кэш-память обычно реализуется в виде ассоциативного ЗУ, в котором для каждой строки сохраняются дополнительные сведения, называемые тегом, или признаком, в качестве которого выступает адресный код или его часть. Когда в АЗУ подается адрес, с ним одновременно сравниваются все теги.

Внутренняя кэш-память в микропроцессоре i486 реализует сквозную запись. Начиная с МП Pentium используется сквозная или обратная запись.

Во внешней КП применяется любой способ записи или их комбинация.

Внутренняя кэш-память МП i486 имеет емкость 8 Кбайт и организована в виде 4-канальной ассоциативной памяти. Это означает, что данные из какой-либо строки ОЗУ могут храниться в любой из 4 строк кэш-памяти.

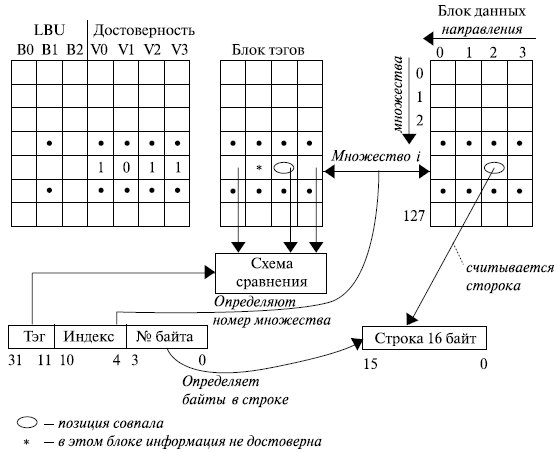

КП состоит из следующих блоков (рис. 4.3):

· блока данных,

· блока тегов,

· блока достоверности и LRU.

Блок данных содержит 8 Кбайт данных и команд. Он разделен на 4 массива (направления), каждый из которых состоит из 128 строк.

Строка содержит данные из 16 последовательных адресов памяти начиная с адреса, кратного 16. Индекс массивов блока данных, состоящий из 7 бит, соответствует 4 строкам КП, по одной из каждого массива. Четыре строки КП с одним и тем же индексом называются множеством.

В блоке тегов имеется один тег длиной 21 бит для каждой строки данных в КП. Блок тегов также разделен на 4 массива по 128 тегов. Тег содержит старшие 21 бит физического адреса данных, находящихся в соответствующей строке КП.

Рис. 3 Структура внутренней кэш-памяти МП i486

В блоке достоверности и LRU содержится по одному 7-разрядному значению для каждого из 128 множеств строк КП: 4 бита достоверности (V) по одному на каждую строку множества и 3 бита (B0 ... B2), управляющие механизмом LRU. Биты достоверности показывают, содержит ли строка достоверные (V = 1) или недостоверные (V = 0) данные. При программной очистке КП и аппаратном сбросе процессора все биты достоверности сбрасываются в 0.

Адресация кэш-памяти осуществляется путем разделения старших 28 бит физического адреса на 2 части. Младшие 7 бит из этих разрядов (разряды 10…4 физического адреса) образуют поле индекса и определяют множество, в котором могут храниться данные. Старшие 21 бит (разряды 31…11 физического адреса) служат полем тега и применяются для определения того, находится ли информация с данным физическим адресом в какой-либо строке выбранного множества.

Поиск в кэш-памяти информации с заданным физическим адресом выполняется следующим образом:

1. Физический адрес, по которому происходит обращение, разбивается на 3 поля: Тег, Индекс, № байта. 7 разрядов А10…А4 поля индекса определяют одно из 128 множеств.

2. В выбранном множестве содержатся 4 строки с информацией.

Чтобы определить, присутствует ли нужная информация в одной из строк этого множества, проводится сравнение старших 21 бита физического адреса (поле Тег) с тегами строк выбранного множества. Сравнение проводится только для достоверных строк, то есть тех, у которых в блоке достоверности установлен бит достоверности V = 1.

3. Если для одной из строк ее тег и разряды А31...А11 физического адреса совпали, то это означает, что произошло кэш-попадание необходимая информация есть в кэш-памяти.

4. Считывается найденная строка из 16 байт. Искомый байт в ней определяется 4 младшими разрядами физического адреса ( А3…А0 ).

5. Если на этапе 3 совпадения не произошло или все строки множества недостоверны, эта ситуация определяется как кэш-промах. В этом случае по сформированному микропроцессором физическому адресу выполняется обращение к оперативной памяти. Из ОЗУ извлекается нужная информация, и содержащая ее строка записывается в свободную строку выбранного множества. Старшие 21бит физического адреса записываются в поле тега этой строки. Если все строки в выбранном множестве достоверны, то замещается строка, к которой дольше всего не было обращений согласно механизму LRU. Этот механизм действует точно так же, как и при вытеснении строк из буфера ассоциативной трансляции TLB.

Режим работы кэш-памяти определяется программно установкой разрядов CD (запрет кэширования) и NW (запрет сквозной записи) в управляющем регистре CR0. Кэширование можно разрешить (это состояние после инициализации при сбросе), можно запретить при наличии достоверных строк (в этом режиме КП действует как быстрое внутреннее ОЗУ) или, наконец, кэширование может быть полностью запрещено.

Контрольные вопросы

1. Как переводится и расшифровывается RAM?

2. Опишите принцип действия ячейки с динамической памяти (DRAM)

3. Опишите принцип действия ячейки статической памяти (SRAM)

4. Как расшифровывается КЭШ?

5. Где располагается кэш-память?

6. Что такое кэш-попадание и кэш-промах?

7. Что такое SIMM –модули и DIMM – модули?

8. Как переводится и расшифровывается ROM?

9. Для чего служит BIOS?

10. Описать организацию внутренней кэш-памяти микропроцессора.

Скачано с www.znanio.ru

Материалы на данной страницы взяты из открытых источников либо размещены пользователем в соответствии с договором-офертой сайта. Вы можете сообщить о нарушении.