ОЦЕНОЧНЫЕ СРЕДСТВА

для межсеместровой аттестации по учебной дисциплине

ОП.08. Архитектура электронно-вычислительных машин и вычислительные системы

Оценочные средства представляют собой банк тестовых заданий для проведения промежуточной аттестации по учебной дисциплине и ориентированы на проверку качества знаний обучающихся, освоивших её полный курс.

К промежуточной аттестации допускаются учащиеся, выполнившие все практические и лабораторные работы.

Содержание банка в полной мере отражает содержание типовой программы учебной дисциплины. В состав банка включают от 30 до 60 тестовых заданий следующих типов:

– задание с выбором одного ответа (закрытой и открытой формы);

– задание с множественным выбором;

– задание на установление правильной последовательности;

– задание на установление соответствия.

К заданиям закрытой формы относятся задания, при выполнении которых тестируемый выбирает правильный (-ые) ответ (-ы) из предложенного набора ответов ( с единичным выбором; с множественным выбором)

К заданиям открытой формы относятся задания, при выполнении которых тестируемый самостоятельно формулирует ответ, регламентированный по содержанию и форме представления ( с регламентированным ответом или свободно конструируемым ответом).

Задания на установление соответствия – это задания, при выполнении которых необходимо установить правильное соответствие между элементами двух множеств: объектов (субъектов, процессов) и их атрибутов (свойств, характеристик, структур и т.п.).

Задания на установление последовательности – это задания, при выполнении которых необходимо установить правильную последовательность действий, событий, операций (порядок среди однородных элементов некоторой группы действий, событий, операций).

В тест включают задания различных уровней трудности. Под трудностью тестового задания понимают количество мыслительных операций и характер логических связей между ними, характеризующих продолжительность поиска и нахождения верного решения.

На трудность тестового задания оказывают влияние следующие факторы:

- количества и характера мыслительных операций, необходимых для выполнения задания;

-формы тестового задания (т.е. способ выражения и передачи тестируемому информации об искомом и предпосылках его нахождения);

- количество вариантов ответов (для тестового задания закрытой формы);

-объем времени отведенный на изучение темы;

- уровень освоения темы или дидактических единиц темы (ознакомительный, репродуктивный, продуктивный).

Время тестирования по одному варианту должно составлять 45 минут.

При оценке результатов за каждый правильный ответ ставится 1 балл,

за неправильный ответ – 0 баллов.

паспорт оценочного средства

|

Результаты обучения (освоенные умения, усвоенные знания) * |

Наименование тем |

Кол-во часов |

Порядковый номер задания |

Уровень трудности ** |

|

Уметь выбирать рациональную конфигурацию оборудования в соответствии с решаемой задачей; |

Тема 1.1. Общие принципы построения современных ЭВМ |

12 |

Практические занятия 1. Составление обобщенной структурной схемы ЭВМ. Состав устройств, их назначение и взаимодействие. |

2-3 |

|

Знать классификацию и типовые узлы вычислительной техники (ВТ); |

||||

|

Уметь обеспечивать совместимость аппаратных и программных средств ВТ. |

Тема 2.1. Системы счисления |

10 |

Практические занятия 2. Решение задач с использованием различных систем счисления. |

2-3 |

|

Знать виды информации и способы ее представления в ЭВМ; |

||||

|

Уметь обеспечивать совместимость аппаратных и программных средств ВТ. |

Тема 2.2. Представление информации в ЭВМ |

8 |

Практические занятия 3. Решение задач: арифметические операции над числами с фиксированной и плавающей точкой в прямом, обратном и дополнительном кодах. |

2-3 |

|

Знать виды информации и способы ее представления в ЭВМ; |

||||

|

Уметь выбирать рациональную конфигурацию оборудования в соответствии с решаемой задачей; |

Тема 2.3 Техническая реализация логических элементов в ЭВМ |

8 |

Практические занятия 4.Использование логических элементов, реализующих функции И, ИЛИ, НЕ. |

2-3 |

|

Знать классификацию и типовые узлы вычислительной техники (ВТ); |

||||

|

Уметь обеспечивать совместимость аппаратных и программных средств ВТ. |

Тема 3.1 Основные функци-ональные элементы ЭВМ.

|

12 |

Практические занятия 5. Построение памяти на RS-триггерах, JK-триггерах. |

2-3 |

|

Знать назначение и принципы действия отдельных архитектурных конфигураций; |

Практические занятия 6. Построение памяти на D-триггерах. |

2-3 |

||

|

Уметь обеспечивать совместимость аппаратных и программных средств ВТ. |

Тема 3.2 Основные функци-ональные элементы

|

6 |

Практические занятия 7. Построение регистров хранения различной разрядности. |

2-3 |

|

Знать назначение и принципы действия отдельных архитектурных конфигураций; |

||||

|

Уметь обеспечивать совместимость аппаратных и программных средств ВТ. |

Тема 3.3 Устройство управления |

6 |

Практические занятия 8. Изучение принципа работы АЛУ при выполнении арифметических действий над числами. |

2-3 |

|

Знать назначение и принципы действия отдельных архитектурных конфигураций; |

||||

|

Уметь выбирать рациональную конфигурацию оборудования в соответствии с решаемой задачей; |

Тема 3.4 Запоминающее устройство

|

6 |

Практические занятия 9. Составление микропрограммы по управлению арифметико-логическим устройством.

|

2-3

|

|

Знать назначение и принципы действия отдельных архитектурных конфигураций; |

||||

|

Уметь обеспечивать совместимость аппаратных и программных средств ВТ. |

Тема 3.5 Запоминающее устройство (ЗУ)

|

8 |

Практические занятия 10. Построение ЗУ заданной организации на БИС ЗУ различного типа. |

2-3

|

|

Знать виды информации и способы ее представления в ЭВМ; |

||||

|

Уметь обеспечивать совместимость аппаратных и программных средств ВТ. |

Тема 4.1. Режимы адресации и форматы команд процессора

|

6 |

Практические занятия 11.Представление команд процессора в машинном виде. |

2-3

|

|

Знать архитектуру электронно-вычислительных машин и вычислительных систем;

|

||||

|

Уметь обеспечивать совместимость аппаратных и программных средств ВТ. |

Тема 4.2 Кодирование команд

|

8 |

Практические занятия 12.Задание режимов адресации 16-разрядного микропроцессора Intel-8086. |

2-3

|

|

Знать архитектуру электронно-вычислительных машин и вычислительных систем;

|

||||

|

Уметь обеспечивать совместимость аппаратных и программных средств ВТ. |

Тема 5.1. Конвейерная организация работы процессора

|

8 |

Практические занятия 13. Изучение порядка взаимодействия УУ, АЛУ и ОЗУ при автоматическом выполнении команд. |

2-3 |

|

Знать назначение и принципы действия отдельных архитектурных конфигураций; |

||||

|

Уметь обеспечивать совместимость аппаратных и программных средств ВТ. |

Тема 5.2 Организация работы мультипрограммных Вычислительных систем

|

6 |

Практические занятия 14.Использование мультипрограммирования при различных режимах работы вычислительных систем |

2-3 |

|

Знать назначение и принципы действия отдельных архитектурных конфигураций; |

||||

|

Знать назначение и принципы действия отдельных архитектурных конфигураций; |

Тема 5.3 Система прерываний. Система управления памятью

|

10 |

Практические занятия 15. Изучение алгоритмов буферизации и кэширования данных. |

2-3 |

|

Уметь обеспечивать совместимость аппаратных и программных средств ВТ. |

2-3 |

|||

|

Знать назначение и принципы действия отдельных архитектурных конфигураций; |

Тема 5.4 Система ввода/вывода информации. |

6 |

Практические занятия 16.Изучение структуры работы контроллера прямого доступа к памяти. |

2-3 |

|

Уметь обеспечивать совместимость аппаратных и программных средств ВТ. |

||||

|

|

|

120 |

|

|

* Указываются требования к умениям и знаниям в соответствии с ФГОС по специальностям, сформулированные в таблице «Структура основной профессиональной образовательной программы, а также те, которые дополнительно определены ГБОУ СПО в соответствии с требованиями работодателей и обучающихся.

**

1- Низкий

2- Средний

3- Высокий

Практические занятия 1

1. Составление обобщенной структурной схемы ЭВМ. Состав устройств, их назначение и взаимодействие

Цель: изучить основные блоки персонального компьютера, способы их соединения, разъемы и их основные характеристики (название, тип разъема, количество контактов, скорость передачи данных, дополнительные свойства); научиться определять компоненты системного блока, искать по ним данные, уяснять порядок и способ их соединения.

1. Разделиться на команды по количеству имеющихся системных блоков, составьте список команд с распределением задач (соответствующая буква в скобках после фамилии (Ж), (И) или (О)) и отдайте преподавателю

Распределение задач в команде:

· Работа с железом – выполняемые пункты отмечены (Ж)

· Поиск информации в книгах и Интернете – выполняемые пункты отмечены (И)

· Написание отчета (желательно в электронном виде, содержание указано в конце данного задания) – выполняемые пункты отмечены (О)

Желательно заранее определить, кто что делает, так как выполнение каждой задачи будет оцениваться отдельно.

2. (Ж) Получить системный блок и инструменты, подготовить рабочее место

3. (Ж), (О) Разобрать системный блок, запоминая или записывая расположение комплектующих (потом его нужно будет собрать). В том числе извлечь материнскую плату и блок питания

4. (Ж) Осторожно очистить комплектующие и системный блок от пыли

5. (О) Записать в отчет названия комплектующих и предоставить их занимающимся поиском данных в Интернете

6. (Ж), (О) Осмотреть комплектующие и системный блок на предмет наличия внешних признаков неисправностей: повреждения, потемневшие детали, вздувшиеся конденсаторы и т.п. В случае наличия подобных признаков – записать их в отчет, в случае отсутствия – записать, что проведен осмотр и внешних признаков повреждений не найдено

7. (И), (О) Поискать в Интернете основные данные по комплектующим, страницы и файлы сохранить для сдачи преподавателю, основные параметры – записать в отчет

8. (Ж), (О) Собрать блок

9. (Ж), (И), (О) Продемонстрировать преподавателю собранный блок и предоставить собранные в Интернете по комплектующим и системному блоку данные и отчет в электронном виде

Примечание: отчет должен быть оформлен в соответствии со стандартами, принятыми для документов в Microsoft Word, в нем должны отсутствовать орфографические и грамматические ошибки.

1. Название команды, список команды с указанием выполняемой задачи каждого участника команды (железо (Ж), интернет (И) или отчет (О))

2. Название системного блока, с которым работала команда

3. Общую информацию по разборке в частности, используемые для комплектующих разъемы (PCI, AGP или PCI-E для видеокарты, сокет микропроцессора и т.п.)

4. Список комплектующих системного блока

5. Данные по внешнему осмотру комплектующих и поиску неисправностей

6. Основные данные по комплектующим:

· название материнской платы, типы и количество основных разъемов (под память, PCI, сокет процессора и т.п.)

· тип и емкость оперативной памяти

· емкость жесткого диска

· тип и частота процессора

· название, слот и объем видеопамяти видеокарты

· типы и количество разъемов на задней (и на передней, если есть) стенке системного блока: PS/2, COM, USB и т.д.

· мощность блока питания, типы и количество имеющихся у него разъемов

Практические занятия 2

2. Решение задач с использованием различных систем счисления

Цель: научиться переводить числа из одной системы счисления в другую.

Задание 1. Запишите развернутую и краткую формы записи любого числа.

Задание 2.

Перевести 10101101.101 из «2» в «16», «8» и «10» с.с.

Задание 3.

Переведите самостоятельно.

а) Перевести 703.048 из «10» в «2», затем в «8» и наконец, в «16»

б) Перевести B2E.416 из «16» в «10», затем в «8».

Задание 4.

а) Перевести 18110 из «10» в «2».

б) Перевести 62210 из «8» в «2», затем в «10».

Задание 5.

Перевести 0.312510

Задание 6. Перевести 0.6510 из «10» в «2» с.с. Точность 6 знаков.

Задание 7.

Перевести 23.12510 из «10» в «2» с.с.

Задание 8.

а)Перевести 305.47 из «8» в «10» с.с.

б)Перевести 7B2.E16 из «16» в «10».

Задание 9.

а) Перевести 1101111001.1101 из «2» в «8» с.с.

б) Перевести 11111111011.100111 из «2» в «16» с.с.

Задание 10.

Перевести 175.248 "16" с.с

Задание 11.

Выполнить сложение двоичных чисел:

а) X=1101, Y=101;

б) X=1101, Y=101, Z=111;

Задание 12.

Заданы двоичные числа X=10010 и Y=101. Вычислить X-Y.

Самостоятельная работа.

Выполнить перевод числа в соответствии с вариантом.

1. Перевести десятичное число А=121 в двоичную систему счисления.

2. Перевести двоичное число А=10001010111,01 в десятичную систему счисления.

3. Перевести десятичное число А=135,656 в двоичную систему счисления с точностью до пяти знаков запятой.

4. Перевести двоичное число А=10111011 в десятичную систему счисления методом деления на основание.

5. Перевести восьмеричное число А=345,766 в двоичную систему счисления.

6. Записать десятичное число А=79,346 в двоичнодесятичной форме.

7. Перевести десятичную дробь 64 A = 63 9 в двоичную систему счисления.

8. Перевести десятичное число А=326 в троичную систему счисления.

9. Перевести десятичную дробь 40 A = 63 5 в двоичную систему счисления.

10. Перевести десятичное число А=15,647 в двоичную систему счисления.

11. Перевести десятичное число А=1211 в пятеричную систему счисления.

12. Перевести десятичную дробь А=0,625 в двоичную систему счисления.

13. Перевести двоичную дробь А=0,1101 в десятичную систему счисления.

14. Перевести десятичное число А=113 в двоичную систему счисления.

15. Перевести двоичное число А=11001,01 в десятичную систему счисления.

16. Перевести десятичное число А=96 в троичную систему счисления.

Практические занятия 3

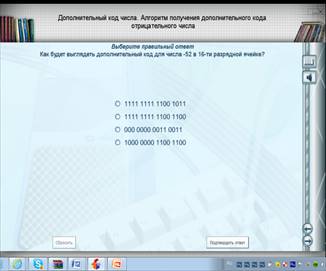

3. Решение задач: арифметические операции над числами с фиксированной и плавающей точкой в прямом, обратном и дополнительном кодах.

Цель урока: иметь представление о форматах чисел с фиксированной и плавающей запятой (точкой), знать понятия прямого кода, обратного кода, дополнительного кода, уметь записывать целые числа (положительные и отрицательные) в прямом, обратном и дополнительном коде.

1. Какие выводы можно сделать из рассмотренных примеров кодирования чисел и арифметических действий с числами? (Оцените удобство выполнения операций).

Сравнение рассмотренных форм кодирования целых чисел со знаком показывает:

· на преобразование отрицательного числа в обратный код компьютер затрачивает меньше времени, чем на преобразование в дополнительный код, так как последнее состоит из двух шагов — образования обратного кода и прибавления единицы к его младшему разряду;

· время выполнения сложения для дополнительных кодов чисел меньше, чем для их обратных кодов, потому что в таком сложении нет переноса единицы из знакового разряда в младший разряд результата.

1. Модуль числа записать в прямом коде в п двоичных разрядах. (Для этого получить внутреннее представление положительного числа N: перевести число N в двоичную систему счисления, полученный результат дополнить слева незначащими нулями до k разрядов)

2. Получить обратный код числа, для этого значения всех битов инвертировать (все единицы заменить на нули и все нули заменить на единицы).

3. К полученному обратному коду прибавить единицу.

3. Назовите алгоритм перевода дополнительного кода в десятичное число

Алгоритм №5 перевода дополнительного кода в десятичное число.

1. Инвертировать дополнительный код

2. Прибавить к полученному коду 1 и получить модуль отрицательного числа:

3. Перевести в десятичное число и приписать знак отрицательного числа.

4. В чем вы видите достоинства представления чисел в формате с фиксированной запятой?

5.Рассмотрите пример записи дополнительного кода отрицательного числа -2002 для 16 разрядного компьютерного представления (учебник, стр. 105). В чем сущность использования дополнительного кода?

Выполнить задания перевести десятичное число в двоичную систему счисления, выполнить сложение, записывая числа в прямом и дополнительном кодах.

Условие: X=A+B, где A= -548, B=292

Решение:

A= -548(10) = ____________________________________________

B=292(10) = ________________________________________________

|

А пк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

А дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

В пк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

В дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

Х пк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

Х дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ответ: |

||||||||||||||||

|

Х дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Выполнить задания: перевести десятичное число в двоичную систему счисления, выполнить сложение, записывая числа в прямом и дополнительном кодах.

Условие: X=A+B, где A= 330, B=-509

Решение:

A= 330(10) = ____________________________________________

B=-509(10) = ________________________________________________

|

А пк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

А дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

В пк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

В дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

Х пк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

Х дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ответ: |

||||||||||||||||

|

Х дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Выполнить задания: перевести десятичное число в двоичную систему счисления, выполнить сложение, записывая числа в прямом и дополнительном кодах.

Условие: X=A+B, где A= 490, B=-491

Решение:

A= 490(10) = ____________________________________________

B=-491(10) = ________________________________________________

|

А пк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

А дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

В пк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

В дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

Х пк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

Х дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ответ: |

||||||||||||||||

|

Х дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Выполнить задания: перевести десятичное число в двоичную систему счисления, выполнить сложение, записывая числа в прямом и дополнительном кодах.

Условие: X=A+B, где A= -256, B=-128

Решение:

A= -256(10) = ____________________________________________

B=-128(10) = ________________________________________________

|

А пк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

А дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

В пк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

В дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

Х пк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

Х дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ответ: |

||||||||||||||||

|

Х дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Выполнить задания: перевести десятичное число в двоичную систему счисления, выполнить сложение, записывая числа в прямом и дополнительном кодах.

Условие: X=A+B, где A= 440, B=-563

Решение:

A= 440(10) = ____________________________________________

B=-563(10) = ________________________________________________

|

А пк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

А дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

В пк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

В дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

Х пк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

Х дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ответ: |

||||||||||||||||

|

Х дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Выполнить задания: перевести десятичное число в двоичную систему счисления, выполнить сложение, записывая числа в прямом и дополнительном кодах.

Условие: X=A+B, где A= -264, B=-336

Решение:

A= -264(10) = ____________________________________________

B=-336(10) = ________________________________________________

|

А пк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

А дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

В пк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

В дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

Х пк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

Х дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ответ: |

||||||||||||||||

|

Х дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Выполнить задания: перевести десятичное число в двоичную систему счисления, выполнить сложение, записывая числа в прямом и дополнительном кодах.

Условие: X=A+B, где A= 268, B=-368

Решение:

A= 268(10) = ____________________________________________

B=-368(10) = ________________________________________________

|

А пк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

А дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

В пк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

В дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

Х пк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

Х дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ответ: |

||||||||||||||||

|

Х дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Выполнить задания: перевести десятичное число в двоичную систему счисления, выполнить сложение, записывая числа в прямом и дополнительном кодах.

Условие: X=A+B, где A= -260, B=-252

Решение:

A= -260(10) = ____________________________________________

B=-252(10) = ________________________________________________

|

А пк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

А дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

В пк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

В дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

Х пк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

Х дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ответ: |

||||||||||||||||

|

Х дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Выполнить задания: перевести десятичное число в двоичную систему счисления, выполнить сложение, записывая числа в прямом и дополнительном кодах.

Условие: X=A+B, где A= 198, B=-580

Решение:

A= 198(10) = ____________________________________________

B=-580(10) = ________________________________________________

|

А пк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

А дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

В пк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

В дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

Х пк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

Х дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ответ: |

||||||||||||||||

|

Х дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Выполнить задания: перевести десятичное число в двоичную систему счисления, выполнить сложение, записывая числа в прямом и дополнительном кодах.

Условие: X=A+B, где A= -222, B=-290

Решение:

A= -220(10) = ____________________________________________

B=-290(10) = ________________________________________________

|

А пк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

А дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

В пк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

В дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

Х пк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

Х дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ответ: |

||||||||||||||||

|

Х дк |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Практическое занятие 5

5.Использование логических элементов, реализующих функции И, ИЛИ, НЕ.

1. На

входы схемы одновременно поступают несколько сигналов. Через какой промежуток

времени на выходе гарантированно появится истинное значение логической функции?

Задержки сигналов при прохождении через логические элементы приведены в таблице

(1нсек=10-9сек).

2. Выберите правильный порядок следования логических элементов. Например: И, ИЛИ, ИСКЛЮЧАЮЩЕЕ ИЛИ.

3. Укажите правильное определение.

1. Функция И равна нулю, если равен нулю только один аргумент.

2. Функция ИЛИ равна нулю, если равен нулю только один аргумент.

3. Функция И равна единице, если равен единице хотя бы один аргумент.

4. Функция И равна нулю, если равен нулю хотя бы один аргумент.

5. Функция ИЛИ равна единице, если равены единице все аргументы.

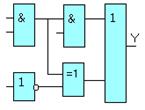

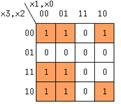

4. Какому уравнению соответствует таблица Карно?

1. Исследование логических элементов И-НЕ, ИЛИ-НЕ

Подключите интегральные схемы серии ТТЛ, реализующие

функции И-НЕ (К155 ЛА3) и ИЛИ-НЕ (К155 ЛЕ1) к источнику питания и исследуйте их

работу. Проверьте выполнение таблицы истинности. Справочная информация по

микросхемам приведена в приложении 1. Подайте на вход одного ЛЭ И-НЕ

прямоугольные импульсы и исследуйте выходные сигналы элемента. Измерьте время

нарастания и время спада выходного напряжения.

^ 5. Реализация функции не (инверсии)

Условное графическое обозначение элемента показано на

рис. 1.2. Синтезируйте и соберите на наборном поле стенда элемент И, используя

элемент 2И-НЕ (возможны 2 варианта). Выход Y соедините с осциллографом.

На вход «а» подайте сигнал логической единицы, а затем - логического

нуля. Зафиксируйте значения выходного сигнала исследуемого элемента. Все

значения входного и соответствующего выходного сигналов занесите в таблицу

истинности. Напишите аналитическое выражение функции и начертите временную

диаграмму для входной и выходной переменных.

^6. Реализация

функции и (конъюнкции)

Условное графическое обозначение элемента показано на

рис. 1.3. Используя в качестве базиса элемент 2И-НЕ синтезируйте и соберите на

наборном поле схему, реализующую функцию И. Выход Y соедините с

осциллографом. Подключая входы «a» и «b» к гнездам «0» и «1» на

вспомогательном устройстве, подайте на входы следующие комбинации сигналов: ![]() Все значения входных и

выходных сигналов занесите в таблицу истинности. Напишите аналитическое

выражение функции и начертите временную диаграмму для входных и выходной

переменных.

Все значения входных и

выходных сигналов занесите в таблицу истинности. Напишите аналитическое

выражение функции и начертите временную диаграмму для входных и выходной

переменных.

^ 7. Реализация

3-х входовой схемы И

Используя в качестве базиса элемент 2И-НЕ синтезируйте и соберите на наборном поле схему, реализующую функцию 3И и исследуйте ее, как это описано в предыдущем пункте задания. Все значения входных и выходных сигналов занесите в таблицу истинности. Напишите аналитическое выражение и составьте временную диаграмму.

8. реализация функции или (дизъюнкции)

Условное графическое обозначение элемента показано на

рис.1.4. Синтезируйте, используя правило Де-Моргана, элемент ИЛИ на базисе

И-НЕ. Соберите синтезированную схему на наборном поле лабораторной установки и

исследуйте ее, как это описано в предыдущем пункте задания. Все значения

входных и выходных сигналов занесите в таблицу истинности. Напишите

аналитическое выражение и составьте временную диаграмму.

9. реализация функции или-не

Условное графическое обозначение элемента показано на

рис.1.5. Для синтеза функции воспользуйтесь результатами предыдущих пунктов

задания. Заполните таблицу истинности полученной комбинационной схемы. Запишите

аналитическое выражение заданной функции и постройте временную диаграмму.

10. реализация функции суммирование по модулю 2

Сумматор по модулю 2 - цифровой узел с m входами и одним выходом. В частном случае при числе входов, равном 2, сумматор по модулю 2 выполняет функцию логического элемента «ИСКЛЮЧАЮЩЕЕ ИЛИ».

Условное графическое обозначение элемента «ИСКЛЮЧАЮЩЕЕ ИЛИ» показано на рис.1.6. На наборном поле собрать схему согласно рис.1.7. Заполните таблицу истинности полученной комбинационной схемы и постройте временную диаграмму. Запишите аналитическое выражение для функции «ИСКЛЮЧАЮЩЕЕ ИЛИ».

^ 8. Реализация функции эквивалентности

Условное графическое обозначение элемента показано на рис.1.8. На наборном поле соберите схему согласно рис.1.9. Заполните таблицу истинности полученной комбинационной схемы и постройте временную диаграмму. Запишите аналитическое выражение для функции «ЭКВИВАЛЕНТНОСТЬ».

Практическое занятие 6

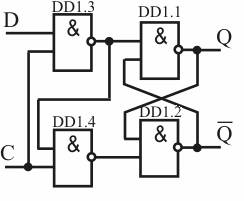

Построение памяти на RS-триггерах, JK-триггерах.

Цели:

1. Изучить общие сведения о JK-триггерах, RS-триггерах.

2. Получить практические навыки по исследованию J К-триггеров, RS-триггерах.

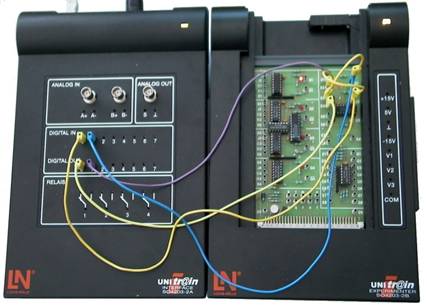

Исследования работы ОУ проводятся на оборудовании UniTrain-I немецкой фирмы LUCAS-NÜLLE GmbH, в состав которого входят базовые блоки Interface (basic VI): SO4203-2A и Experimenter SO4203-2B, а также сменная плата: SO4201-9T

Рис. 7 Базовые блоки. Коммутация элементов схемы.

Рассмотрим структуру сменной платы и принципиальные схемы ее частей.

|

|

· 4 JK триггера (ряд ИС слева) · 4 элемента И-НЕ 74HC00N (справа вверху) · 8 инверторов НЕ 74HC04N (справа внизу)

1. Соединяя триггеры с элементами И-НЕ и инверторами можно собрать счетчики (синхронный, асинхронный, прямого и обратного счета т.д.), регистры (параллельный, последовательный или кольцевого типа) и делитель частоты. 2. Состояние выходного сигнала триггера Q можно увидеть с помощью индикатором на светодиоде. 3. Если на входах триггеров и схем НЕ - И нет сигналов, то их выходы находятся в состоянии «высокий уровень». И наоборот, разрыв на входе инверторов (НЕ) приводит их в состоянии «низкий уровень».

|

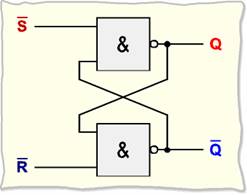

RS триггер.

Рис. 8 Простой RS триггер на элементах И-НЕ. RS триггер со сбросом (справа).

1. Для исследования работы простого RS триггер соедините проводами следующие гнезда

|

Источник / приемник |

Точка схемы |

|

Цифровой выход 1 |

Терминал И-НЕ: E1 |

|

Цифровой выход 0 |

Терминал И-НЕ: E4 |

|

Цифровой Вход 1 |

Терминал И-НЕ: Q1 |

|

Цифровой Вход 0 |

Терминал И-НЕ: Q2 |

|

Терминал И-НЕ: E2 |

Терминал И-НЕ: Q2 |

|

Терминал И-НЕ: E3 |

Терминал И-НЕ: Q1 |

2. Запустите программу VI Starter. В трее появиться желтый значок в виде «i» для вызова виртуальных приборов и источников сигналов.

3. В меню Instruments программы VI Starter выберите следующие инструменты

|

Инструмент |

Примечание |

|

Цифровые Входы и Выходы (Digital IO Display) |

Q0 и Q1 – выходы (digital out) I0 и I1 – индикаторы выходов (digital in) |

4. Заполните следующую таблицу, где Qn и Qn+1 состояние выходов триггера ДО и ПОСЛЕ установки сигналов на входе.

Q0 и Q1 – выходы виртуального инструмента «Цифровые Входы и Выходы» (Digital IO Display) I0 и I1 – индикаторы выходов на этом инструменте.

|

вход S |

вход R |

прямой выход Qn |

прямой выход Qn+1 |

инверсный выход Qn+1 |

|

Q1 |

Q0 |

I1 |

I1 |

I0 |

|

0 |

0 |

0 |

|

|

|

0 |

0 |

1 |

|

|

|

0 |

1 |

0 |

|

|

|

0 |

1 |

1 |

|

|

|

1 |

0 |

0 |

|

|

|

1 |

0 |

1 |

|

|

|

1 |

1 |

0 |

|

|

|

1 |

1 |

1 |

|

|

Необходимое состояние прямого выхода Qn установите, манипулируя выходами виртуального инструмента Q0 и Q1.

5. Для исследования работы RS триггер со сбросом соедините проводами следующие гнезда

|

Источник / приемник |

Точка схемы |

|

Цифровой выход 1 |

Терминал И-НЕ: E5 |

|

Цифровой выход 0 |

Терминал НЕ: E1 |

|

Терминал НЕ: Q1 |

Терминал И-НЕ: E4 |

|

Терминал НЕ: Q1 |

Терминал И-НЕ: E6 |

|

Терминал НЕ: Q3 |

Терминал И-НЕ: E1 |

|

Терминал И-НЕ: E2 |

Терминал И-НЕ: Q2 |

|

Терминал И-НЕ: E3 |

Терминал И-НЕ: Q1 |

|

Цифровой Вход 1 |

Терминал И-НЕ: Q1 |

|

Цифровой Вход 0 |

Терминал И-НЕ: Q2 |

6. Заполните следующую таблицу, где Qn и Qn+1 состояние выходов триггера ДО и ПОСЛЕ установки сигналов на входе. Z1 и Z2 – контрольные точки схемы

Q0 и Q1 – выходы виртуального инструмента «Цифровые Входы и Выходы» (Digital IO Display) I0 и I1 – индикаторы выходов на этом инструменте.

|

вход S |

вход R |

прямой выход Qn |

Z1 |

Z2 |

прямой выход Qn+1 |

инверсный выход Qn+1 |

|

Q1 |

Q0 |

I1 |

I3 |

I2 |

I1 |

I0 |

|

0 |

0 |

0 |

|

|

|

|

|

0 |

0 |

1 |

|

|

|

|

|

0 |

1 |

0 |

|

|

|

|

|

0 |

1 |

1 |

|

|

|

|

|

1 |

0 |

0 |

|

|

|

|

|

1 |

0 |

1 |

|

|

|

|

|

1 |

1 |

0 |

|

|

|

|

|

1 |

1 |

1 |

|

|

|

|

Необходимое состояние прямого выхода Qn установите, манипулируя выходами виртуального инструмента Q0 и Q1.

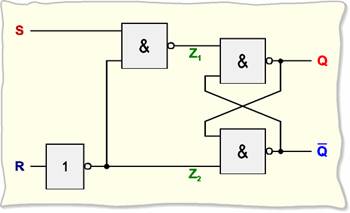

D-триггер синхронизируемый уровнем

Рис. 9 D- триггер на элементах И-НЕ. Вход данных D, тактовый вход C.

1. Для исследования работы простого D- триггера соедините проводами следующие гнезда

|

Источник / приемник |

Точка схемы |

|

Терминал И-НЕ: E2 |

Терминал И-НЕ: Q2 |

|

Терминал И-НЕ: E3 |

Терминал И-НЕ: Q1 |

|

Терминал И-НЕ: E1 |

Терминал И-НЕ: Q3 |

|

Терминал И-НЕ: E4 |

Терминал И-НЕ: Q4 |

|

Терминал И-НЕ: E7 |

Терминал И-НЕ: Q3 |

|

Терминал И-НЕ: E6 |

Терминал И-НЕ: E8 |

|

Цифровой выход 1 |

Терминал И-НЕ: E5 |

|

Цифровой выход 0 |

Терминал И-НЕ: E8 |

|

Цифровой Вход 1 |

Терминал И-НЕ: Q1 |

|

Цифровой Вход 0 |

Терминал И-НЕ: Q2 |

2. Запустите программу VI Starter. В трее появиться желтый значок в виде «i» для вызова виртуальных приборов и источников сигналов.

3. В меню Instruments программы VI Starter выберите следующие инструменты

|

Инструмент |

Примечание |

|

Цифровые Входы и Выходы (Digital IO Display) |

Q0 и Q1 – выходы (digital out) I0 и I1 – индикаторы выходов (digital in) |

4. Заполните следующую таблицу, где Qn и Qn+1 состояние выходов триггера ДО и ПОСЛЕ установки сигналов на входе.

Q0 и Q1 – выходы виртуального инструмента «Цифровые Входы и Выходы» (Digital IO Display) I0 и I1 – индикаторы выходов на этом инструменте.

|

вход S |

вход R |

прямой выход Qn |

прямой выход Qn+1 |

инверсный выход Qn+1 |

|

Q1 |

Q0 |

I1 |

I1 |

I0 |

|

0 |

0 |

0 |

|

|

|

0 |

0 |

1 |

|

|

|

0 |

1 |

0 |

|

|

|

0 |

1 |

1 |

|

|

|

1 |

0 |

0 |

|

|

|

1 |

0 |

1 |

|

|

|

1 |

1 |

0 |

|

|

|

1 |

1 |

1 |

|

|

Необходимое состояние прямого выхода Qn установите, манипулируя выходами виртуального инструмента Q0 и Q1.

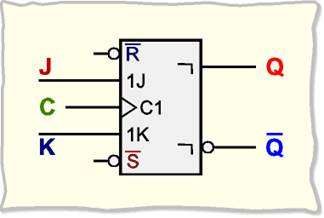

Рис. 10 Условное обозначение JK триггера.

1. Для исследования работы JK- триггера соедините проводами следующие гнезда

|

Источник / приемник |

Точка схемы |

|

Цифровой Выход 4 |

Tерминал FF S1 |

|

Цифровой Выход 3 |

Tерминал FF J1 |

|

Цифровой Выход 2 |

Tерминал FF C1 |

|

Цифровой Выход 1 |

Tерминал FF K1 |

|

Цифровой Выход 0 |

Tерминал FF R1 |

|

Цифровой Вход 1 |

Tерминал FF Q1 |

|

Цифровой Вход 0 |

Tерминал FF Q1 |

2. Запустите программу VI Starter. В трее появиться желтый значок в виде «i» для вызова виртуальных приборов и источников сигналов.

3. В меню Instruments программы VI Starter выберите следующие инструменты

|

Инструмент |

Примечание |

|

Цифровые Входы и Выходы (Digital IO Display) |

Q0 и Q1 – выходы (digital out) I0 и I1 – индикаторы выходов (digital in) |

4. Проверьте возможность управления JK –триггером с помощью

нетактируемыми входами S и R («Цифровые Выходы 4 и 0»

виртуального инструмента) в соответствии с таблицей:

|

S |

R |

Qn+1 |

Qn+1 |

режим |

|

1 |

1 |

Q |

Q |

хранение |

|

0 |

1 |

1 |

0 |

установка |

|

1 |

0 |

0 |

1 |

сброс |

|

0 |

0 |

1 |

0 |

|

5. Изучите работу JK –триггера во всех 4 режимах:

· J=0 и K=0;

· J=1 и K=0;

· J=0 и K=1;

· J=1 и K=1;

6. Перед каждым упражнением установите триггер в состояние Q=1 при помощи сигналов S=0 и R=1, после чего установите режим хранения S=1 и R=1.

7. Установите необходимые уровни сигналов на J и K («Цифровые Выходы 3 и 1» виртуального инструмента).

8. Подайте импульс на вход C импульс, дважды нажимая на кнопку виртуального прибора «Цифровые Выходы 3»

9. Заполните следующую таблицу, где Qn и Qn+1 состояние выходов триггера ДО и ПОСЛЕ подачи импульса на вход C.

|

J |

K |

C |

Qn |

Qn+1 |

Qn+1 |

|

0 |

0 |

|

0 |

|

|

|

0 |

0 |

|

1 |

|

|

|

0 |

1 |

|

0 |

|

|

|

0 |

1 |

|

1 |

|

|

|

1 |

0 |

|

0 |

|

|

|

1 |

0 |

|

1 |

|

|

|

1 |

1 |

|

0 |

|

|

|

1 |

1 |

|

1 |

|

|

Необходимое состояние прямого выхода Qn установите, манипулируя входами S и R.

10. Оформите отчет, сделайте выводы.

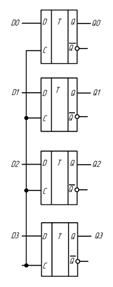

Практическое занятие 7

Построение памяти на D-триггерах.

Целью лабораторной работы является получение практических навыков в построении и контроле работоспособности триггеров D-, а также исследование логики работы триггеров в различных режимах методом моделирования с использованием программы Electronics Workbench.

Задание 1. Построить на элементах 2И-НЕ и 2ИЛИ-НЕ схемы асинхронных RS-

триггеров (см. рисунок 6.3) и исследовать логику их работы в статическом режиме. Для этого собрать схемы с использованием пробников и переключателей.

Путем моделирования работы триггеров получить таблицы переходов и сравнить их с таблицей 6.1. Образцы схем для моделирования приведены на рисунке 6.15. Исследуемые схемы и таблицы занести в отчет.

Задание 2. Построить на элементах 2И-НЕ и 2-2И-2ИЛИ-НЕ схемы синхронных RS- триггеров (см. рисунок 6.4) и исследовать логику их работы в статическом режиме. Образцы схем для моделирования приведены на рисунке 6.16 и 6.17. В качестве элементов 2-2И-2ИЛИ-НЕ использована микросхема 7455, в которой располагается элемент 4-4И-2ИЛИ-НЕ. Исследуемые схемы и таблицы занести в отчет.

Задание 3. Исследовать в статическом режиме логику работы RS-триггера, который имеется в библиотеке программы. Для этого собрать схему, показанную на рисунке 6.18. Получить таблицу переходов триггера и сравнить ее с таблицей 6.1. Исследуемую схему и таблицу занести в отчет.

Задание 4. Исследовать в статическом режиме логику работы двухтактного RS-триггера. Для этого собрать схему, показанную на рисунке 6.19. Получить таблицу переходов триггера и сравнить ее с таблицей 6.1. Исследуемую схему и таблицу занести в отчет.

Задание 5. Исследовать в статическом режиме логику работы асинхронного D-триггера. Для этого собрать схему, показанную на рисунке 6.20. Получить таблицу переходов триггера и сравнить ее с таблицей 6.3. Исследуемую схему и таблицу занести в отчет.

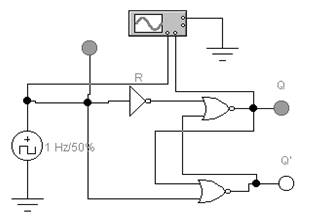

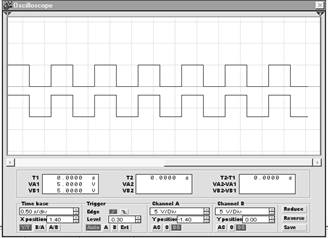

Задание 6. Исследовать в динамическом режиме логику работы асинхронного D-триггера. Для этого собрать схему, показанную на рисунке 6.21. Для визуального наблюдения работы схемы установить частоту генератора 1 Гц. Зарисовать полученную осциллограмму. Исследуемую схему и таблицу занести в отчет.

Задание 7. Собрать и исследовать в статическом режиме схему синхронного D- триггера на элементе 2И-2И-2ИЛИ-НЕ, в качестве которого использовать

микросхему 7451 с 2-мя элементами 2И-2И-2ИЛИ-НЕ. Схема для исследования показана на рисунке 6.22. Результаты исследования занести в отчет.

Задание 8. Собрать и исследовать микросхему 7474, состоящую из 2-х синхронных D-триггеров. Схема показана на рисунке 6.23. Результаты исследования занести в отчет.

Задание 9. Собрать схему и исследовать работу асинхронного Т-триггера, построенного на базе синхронного D-триггера в статическом режиме. Соответст-

|

|||

|

|||

вующая схема показана на рисунке 6.24. В качестве синхронного D-триггера использовать микросхему 7474 с дополнительными асинхронными входами установки и сброса (инверсные входы R и S). Результаты исследования занести в отчет.

Задание 10. Исследовать работу синхронного JK-триггера в динамическом режиме. Для этого собрать схему, показанную на рисунке 6.25. При подаче на

входы J и K сигналов высокого уровня, а на вход синхронизации импульсов от генератора, триггер будет работать в режиме переключения с частотой в два раза ниже, чем частота генератора. Для визуальной индикации подключить осциллограф к выходам генератора и триггера.

|

Задание 11. Собрать схему и исследовать работу синхронного JK-триггера в статическом режиме. Соответствующая схема показана на рисунке 6.26. В качестве синхронного JK-триггера использовать микросхему 74112. Результаты исследования занести в отчет.

Практические занятия 8

8. Построение регистров хранения различной разрядности

Цель работы: Целью работы является изучение принципа работы схем триггерных регистров и приобретение практических навыков в выполнении микроопераций на регистрах в статическом режиме.

2 Краткие теоретические сведения

Регистры предназначены для хранения и преобразования многоразрядных двоичных чисел. Для запоминания отдельных разрядов числа могут применяться триггеры различных типов. Одиночный триггер можно считать одноразрядным регистром.

Занесение информации в регистр называется операцией записи. Операция выдачи информации из регистра – считывание.

Перед записью информации в регистр, его необходимо обнулить.

Классификация регистров:

1 по способу ввода/вывода информации:

· параллельные (регистры хранения) – информация вводится и выводится одновременно по всем разрядам;

· последовательные (регистры сдвига) – информация бит за битом «проталкивается» через регистр и выводится также последовательно;

· комбинированные – параллельный ввод и последовательный вывод (и наоборот).

2 по способу представления информации:

· однофазные – информация представляется в прямом или обратном (инверсном) виде;

· парафазные – информация представляется и в прямом, и в обратном виде.

2.1 Параллельный регистр

Параллельные регистры осуществляют прием и выдачу информации в параллельном коде, а это значит, что для передачи каждого разряда используется отдельная линия.

Для записи информации в регистр на его входных выводах (D0-D3) нужно установить логические уровни, после чего на вход синхронизации (C) подать разрешающий импульс — логическую единицу. После этого на выходах Q0-Q3 появится записанное слово. Регистры запоминают входные сигналы только в момент времени, определяемый сигналом синхронизации.

Рисунок 2.1 – Условно-графическое обозначение параллельного регистра

Рисунок 2.2 – Схема параллельного регистра

2.1 Последовательные регистры

Кроме параллельного соединения триггеров для построения регистров используются последовательное соединение этих элементов.

Последовательный регистр (регистр сдвига) обычно служит для преобразования последовательного кода в параллельный и наоборот. Применение последовательного кода связано с необходимостью передачи большого количества двоичной информации по ограниченному количеству соединительных линий. При параллельной передаче разрядов требуется большое количество соединительных проводников. Если двоичные разряды последовательно бит за битом передавать по одному проводнику, то можно значительно сократить размеры соединительных линий на плате (и размеры корпусов микросхем).

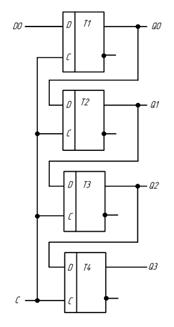

Принципиальная схема последовательного регистра, собранного на основе D-триггеров и позволяющего осуществить преобразование последовательного кода в параллельный, приведена на рисунке 2.3.

Рассмотрим работу этого регистра.

Можно предположить, что в начале все триггеры регистра находятся в состоянии

логического нуля, т.е. Q0=0, Q1=0, Q2=0, Q3=0. Если на входе D-триггера Т1

имеет место логический 0, то поступление синхроимпульсов на входы «С» триггеров

не меняет их состояния.

Рисунок 2.3 – Схема последовательного регистра

Как следует из рисунка 2.3, синхроимпульсы поступают на соответствующие входы всех триггеров регистра одновременно и записывают в них то, что имеет место на их информационных входах. На информационных входах триггеров Т2, Т3, Т4 – уровни логического «0», т.к. информационные входы последующих триггеров соединены с выходами предыдущих триггеров, находящихся в состоянии логического «0», а на вход «D» первого триггера, по условию примера, подается «0» из внешнего источника информации. При подаче на вход «D» первого триггера «1», с приходом первого синхроимпульса, в этот триггер запишется «1», а в остальные триггеры – «0», т.к. к моменту поступления фронта синхроимпульса на выходе триггера Т1 ещё присутствовал логический «0». Таким образом, в триггер Т1 записывается та информация (тот бит), которая была на его входе «D в момент поступления фронта синхроимпульса и т.д.

При поступлении второго синхроимпульса логическая «1» с выхода первого триггера, запишется во второй триггер, и в результате происходит сдвиг первоначально записанной «1» с триггера Т1 в триггер Т2, из триггера Т2 в триггер Т3 и т.д. Таким образом, производится последовательный сдвиг поступающей на вход регистра информации (в последовательном коде) на один разряд вправо в каждом такте синхроимпульсов.

После поступления четырёх синхроимпульсов регистр оказывается полностью заполненным разрядами числа, вводимого через последовательный ввод «D». В течение следующих четырёх синхроимпульсов производится последовательный поразрядный вывод из регистра записанного числа, после чего регистр оказывается полностью очищенным (регистр окажется полностью очищенным только при условии подачи на его вход уровня «0» в режиме вывода записанного числа).

Рисунок 2.4 – Временные диаграммы, поясняющие работу регистра сдвига

3 Задание к работе

3.1 Исследовать параллельный регистр

Сконфигурировать ПЛИС в соответствии с рисунком 3.1.

Рисунок 3.1 – Схема 4-х битного параллельного регистра

Записать целые десятичные числа от 0 до 15 в двоичной системе счисления в регистр и считать их. Заполнить таблицу 3.1.

Таблица 3.1 – Коды, записанные в параллельный регистр

|

Записываемое десятичное число |

Считанное из регистра двоичное число |

|

0 |

|

|

1 |

|

|

... |

|

|

15 |

|

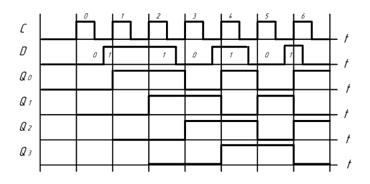

3.2 Исследовать последовательно-параллельный регистр

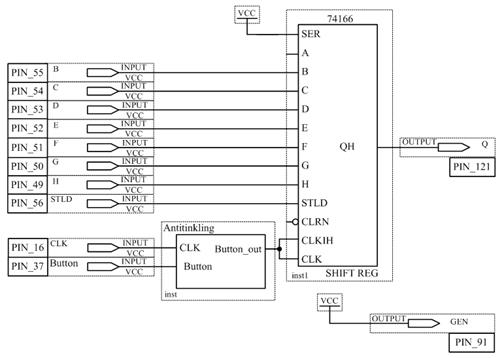

Сконфигурировать ПЛИС в соответствии с рисунком 3.2.

Рисунок 3.2 – Схема последовательно-параллельного регистра

Элемент 74164 – это последовательно-параллельный регистр.

ВНИМАНИЕ! Для того, что бы выполнить блок Antitinkling, прочтите инструкцию Борьба с дребезгом контактов.

Записать нечётное число в интервале от 32 до 56 в последовательном коде, поразрядно продвигая его влево путём нажатия кнопки Button. Записать результат в отчёт.

3.3 Исследовать параллельно-последовательный регистр

Сконфигурировать ПЛИС в соответствии с рисунком 3.3.

Рисунок 3.3 – Схема параллельно-последовательного регистра

Элемент 74166 представляет собой параллельно-последовательный регистр.

Чтобы записать на входе число необходимо установить на входе STLD логический 0 и подать синхроимпульс, чтобы начать считывать записанное число необходимо на вход STLD подать логическую 1 и подавать синхроимпульсы.

Записать число в интервале от 32 до 56 в параллельном коде и поразрядно считывать его на выходе. Записать результат в отчёт.

4 Содержание отчёта

4.1 Цель работы.

4.2 Схема исследования параллельного 4-х битного регистра с таблицей 3.1 .

4.3 Схема последовательно-параллельного регистра с результатами исследований.

4.4 Выводы по каждому заданию.

5 Контрольные вопросы

5.1 Назначение регистров.

5.2 По каким признакам классифицируются регистры?

5.3 Чем определяется разрядность регистров?

5.4 Назначение параллельного регистра.

5.5 Объяснить принцип работы последовательного регистра.

5.6 Объяснить принцип работы параллельного регистра.

5.7 Объяснить принцип работы последовательно-параллельного регистра.

5.8 Объяснить принцип работы параллельно-последовательного регистра.

Практические занятия 9

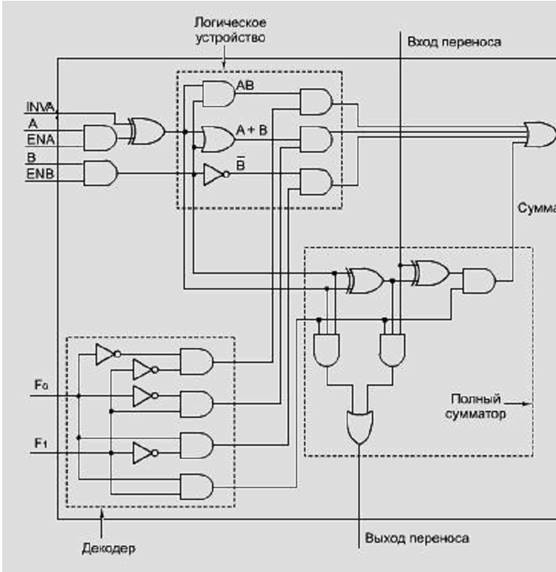

9. Изучение принципа работы АЛУ при выполнении арифметических действий над числами

Цель работы: Изучение принципов построения и функционирования АЛУ для выполнения логических операций.

Задание.

1. Изучить принципы работы отдельных триггерных групп в АЛУ:

s логическое устройство;

s декодер;

s полный сумматор.

2. Составить таблицы истинности для каждой группы.

3. Изучить принцип действия АЛУ, задав А=0, В=1.

Контрольные вопросы:

1. Определение АЛУ.

2. Состав АЛУ.

3. Операции, выполняемые АЛУ.

4. Классификация АЛУ.

5. Инверсия.

6. Конъюнкция.

7. Дизъюнкция.

8. Сложение по модулю 2.

Практические занятия 10

10. Составление микропрограммы по управлению арифметико-логическим устройством

Цель работы

1. Разработка графа микропрограммы вычислительной процедуры машинной операции для заданной системы микрокоманд.

2. Синтез управляющего автомата для реализации микропрограммы.

Задания:

1. Ознакомиться с содержанием лабораторной работы и индивидуальным заданием к ней.

2. В соответствии с индивидуальным заданием выполнить следующие этапы синтеза управляющего автомата:

· разработать граф микропрограммы вычислительной процедуры;

· построить ГСА работы управляющего автомата и соответствующий ему граф автомата Мили (Мура);

· произвести кодирование состояний автомата и составить структурную таблицу;

· определить логические выражения для выходных сигналов управления и сигналов возбуждения триггера;

· построить структурную схему автомата.

3. Преобразовать логические выражения для комбинационной части автомата к виду, соответствующему выбранному типу логических элементов.

4. Построить схему управляющего автомата.

Рис. 4.12 Структурная схема управляющего автомата Мура

5. Собрать схему автомата и произвести ее исследование на предмет правильности интерпретации автоматом граф- схемы алгоритма ГСА. Результатом исследования должна стать временная диаграмма, интерпретирующая ГСА в тактах управляющего автомата для нескольких комбинаций признаков из множества X, как это показано на рис. 4.13.

6. Отчет должен содержать этапы синтеза УА, его схему и временные диаграммы исследования его работы.

7.

Рис. 4.13 Временная диаграмма интерпретации ГСА рис.4.5,а

автоматом Мили

Индивидуальные задания к работе

Индивидуальное задания к работе определяется функцией, микропрограмму выполнения которой надо реализовать на рассмотренном операционном устройстве (рис. 4.2) под управлением спроектированного управляющего автомата. Считать, что операнды функции находятся в регистрах РОН, а результат вычислений помещается в аккумулятор.

ПОЯСНЕНИЯ к заданию 2 и 3:

В регистрах РОН находятся маски D и T, выбранные следующим образом:

· маска ^ D предназначена для селективного сброса битов в тех разрядах регистра РОН с вектором входных переменных X={x7, x6, ..., x0}, номера которых соответствуют отсутствующим переменным в исходном терме;

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

·

маска Т включает «1» в позициях, которые соответствуют переменным без

инверсии в исходном терме и «0» в остальных позициях.

Процедура вычисления заканчивается проверкой соотношения:

![]()

В задании 3 маска ^ D выбирается так же, а маска T включает «1» в позициях, соответствующих инверсным переменным, а в остальных - нули. Процедура заканчивается проверкой соотношения:

![]()

Практические занятия 11

11. Построение ЗУ заданной организации на БИС ЗУ различного типа

Цель работы

Целью лабораторной работы является исследование комплекса характеристик производительности и стоимости компьютера, имеющего иерархическую структуру памяти, включающую кэш память, основную память и внешнее ЗУ. В процессе исследования учитываются параметры выполняемой компьютером задачи.

Задание

Число независимых переменных N=33, параметр k=10, стоимость вычислений P=110.

1) Используя первый раздел меню «Оценка характеристик задачи» провести оценку длительности выполнения программы, определяемую числом циклов выполнения команд программы. Исходные значения числа независимых переменных для создаваемого программного обеспечения выбрать в соответствии с заданием. При определении оценки сложности структуры данных и сложности алгоритма обработки данных подтвердить предлагаемые программой варианты нажатием клавиши «Ввод».

2) Используя второй раздел меню «Расчет характеристик процессора» исследовать изменение характеристик быстродействия (рабочей частоты процессора), надежности (времени наработки на отказ) и стоимости процессора в зависимости от используемых в нем логических БИС (вспомнить результаты работы N1).

Выбрать наиболее дешевый процессор из исследованных вариантов и использовать его в последующих расчетах вычислительной системы.

3) Используя третий раздел меню “Расчет характеристик памяти” задать объем оперативной памяти 32 МБ (8М*32 разряда) и время выборки 70нс, а затем подобрать микросхему памяти определенной емкости для создания:

а) ЗУ максимальной надежности;

б) ЗУ минимальной стоимости.

Для дальнейших расчетов использовать вариант ЗУ с минимальной стоимостью.

4) Используя четвертый раздел меню «Расчет характеристик компьютера» оценить влияние на длительность выполнения задания, производительность и стоимость ВС и стоимость вычислений изменения характеристик кэш-памяти. Объем кэш-памяти изменять в интервале 0 - 32 КБ (0,4,8, 16, 32К), время выборки кэш-памяти в интервале от 10 до 30 нс. (10, 20, 30 ). Считать, что программа не использует ВЗУ. Результаты исследования свести в две таблицы.

Изменяя емкость кэш-памяти при времени выборки для нее 20 нс. найти вариант вычислительной системы (ВС) с минимальной стоимостью вычислений. Объяснить качественно полученный результат.

5) Оценить влияние на длительность выполнения задания, производительность и стоимость ВС длительности цикла обращения к ВЗУ и числа обращений при выполнении задания. Изменять число обращений от 1 до 6 при длительности цикла обращения 15 и 20 мс. Результаты свести в две таблицы.

6) Используя возможности программы синтезировать вариант компьютера (выбрать процессор, микросхему памяти, кэш), обеспечивающего выполнение задания, сложность которого описывается выражением k*n**2, а значения параметра k и числа переменных n приведены в таблице 2 в соответствии с номером варианта. Синтезированный вариант компьютера должен обеспечивать стоимость вычислений Р равную или меньшую значения, указанного в задании. Выбирать для процессора базовый коэффициент дефектности равным 1.0 деф/см2, площадь кристалла 1.0 см2, и объем процессора в 250 тыс.ЛЭ; объем оперативной памяти 2М*32 разряда (8 МБ); к ВЗУ емкостью 500 Мбайт и временем доступа 15мс производится 2 обращения. Время выборки кэш-памяти изменять в пределах 10 - 30 нс.

Практические занятия 12

12.Представление команд процессора в машинном виде

Цель работы Получение начальных сведений о низкоуровневом программировании центрального процессора и памяти вычислительной системы.

Задание к лабораторной работе

1. Внимательно изучить текст функции asmfunc, приведенной в указаниях к лабораторной работе и определить ее назначение.

2. Написать функцию на языке С++, которая выполняет действия, аналогичные функции asmfunc.

3. Сравнить быстродействие функций asmfunc и аналогичной функции на языке C++. Для этого замерить время выполнения каждой функции, управляя значениями следующих параметров: 1) длина строки S; 2) количество последовательных повторных вызовов каждой функции. Сделать выводы по проведенному исследованию.

4. С использованием технологии ассемблерных вставок реализовать функцию по заданию своего варианта. Требования к функции и к программе в целом:

· Ввод данных реализовывать средствами языка С++.

· Вывод информации на экран реализовывать средствами языка ассемблера, если иное не указано в задании. Для упрощения алгоритма вывода на экран числовой информации использовать шестнадцатеричную систему счисления. Рекомендуется организовать алгоритм вывода чисел в отдельной функции.

· В начале работы программы средствами языка ассемблера предлагать пользователю очистить экран и очищать его при необходимости.

· Не завершать работу программы до тех пор, пока пользователь не нажмет клавишу на клавиатуре. Чтение символа с клавиатуры реализовать командами языка ассемблера.

5. В отчете к лабораторной работе отразить ход выполнения работы, привести текст соответствующих программных процедур, изложить сделанные выводы.

Варианты заданий

1. Вывод на экран строки символов. Входные параметры функции: char *S – строка для вывода на экран, char tc – символ, обозначающий конец строки, int sl – флаг вывода длины. Если sl <> 0, то после вывода строки выводить на экран ее длину.

2. Проверка неравенства треугольника. Входные параметры функции: int a,b, c - длины сторон треугольника. Если составить треугольник можно, то возвращать 0. В противном случае возвращать -1 и выводить на экран нарушенное неравенство в форме:

[Длина стороны 1] «+»[Длина стороны 2] «<»[Длина стороны 3].

3. Выбор из трех чисел двух таких, разность которых будет максимальной. Входные параметры функции: int a, b, c – произвольные числа. Форма вывода результата:

[Число 1] «пробел»[Число 2]

4. Нахождение N-го члена арифметической прогрессии. Входные параметры функции: int A – первый член прогрессии, int b – разность прогрессии, int N – номер искомого члена. Вывести на экран результат работы функции.

5. Нахождение в заданной строке символа с наибольшим ASCII-кодом. Входные параметры функции: char *S – строка для поиска, int n – длина строки. Вывести на экран найденный символ и его ASCII-код.

6. Подсчет в заданной строке количества вхождений некоторого символа. Входные параметры функции: char *S – строка, int n – длина строки, char c – искомый символ. Вывести на экран количество найденных символов.

7. Нахождение суммы максимального и минимального элементов в массиве чисел. Входные параметры функции: int A – массив чисел, int n – длина массива. Вывести на экран результат работы функции.

8. Отсортировать по возрастанию заданный массив чисел. Входные параметры функции: int *A – массив чисел, int n – длина массива. Вывод информации в основной программе осуществлять средствами языка C++.

1. Понятие машинно-ориентированных языков.

2. Достоинства и недостатки языков высокого уровня и языков ассемблера.

3. Регистры общего назначения МПП.

4. Сегментные регистры МПП.

5. Регистры-указатели МПП.

6. Регистр флагов МПП.

7. Адресация памяти при работе микропроцессора в реальном режиме.

8. Понятие и виды прерываний.

9. Прямая и косвенная адресация операндов в инструкциях языка ассемблера.

10. Команды передачи управления в языке ассемблера.

11. Способы задания циклов в языке ассемблера.

12. Какое максимальное количество оперативной памяти доступно процессорам семейства Intel x86 при работе в реальном режиме?

Практические занятия 13

13.Задание режимов адресации 16-разрядного микропроцессора Intel-8086.

Цель работы

Целью работы является исследование архитектурных характеристик от-

дельных микропроцессоров и приобретение навыков записи программ в мне-

мокодах и машинных кодах

Познакомьтесь с функциями и форматом следующих команд от-

ладчика: дамп (d), ввод (e), шестнадцатеричный (h), выход (q), регистры (r),

трассировка( t).

20

1.3.2 Загрузите DEBUG. После приглашения к диалогу с помощью ко-

манды d определите:

а) размер памяти (ячейки 413h и 414h)

-d 0040:0013 <enter>

б) серийный номер

-d fe00:0 <enter>

в) дату ROM BIOS в формате mm/dd/yy по адресу FFFF5

Данные запишите в отчёт.

1.3.3 Наберите программу в машинных кодах (см. таблицу 1.2) с шага

CS:100, набирая побайтно через пробел:

-e cs:100 b8 23 ……….. cb <enter>

Выполните программу по шагам, используя команды отладчика R и T.

При этом наблюдайте как изменяется содержимое регистров микропроцессора:

-r <enter>

-t <enter>

.

.

. до команды RETF

Таблица 1.2 - Пример программы в машинных кодах

Машинный код

Команды

Мнемокод

(ассемблер)

Назначение

Команды

B82301

052500

8bd8

03d8

8bcb

90

Cb

Заполните графы таблицы 1.2 "мнемокод" и "назначение".

1.3.4 Исследуйте команду отладчика H. Возьмите несколько значений

(<значение1> и <значение2>) и объясните результаты.

1.3.5 Изучите команду отладчика A. Выпишите в отчёт все фрагменты

ассемблерных программ пп. 1.2.4 и 1.2.6 методического указания к данной ла-

бораторной работе, введите их в DEBUG, выполните по шагам, наблюдая за

измением всех компонент МП, используемых в данном фрагменте, и напишите

комментарий к каждой команде по следующему образцу:

-A cs:100 <enter>

1D60:0100 mov ax,5

1D60:0103 mov dx,9

1D60:0106 add ax,dx

1D60:0108

21

-r

AX=0000 BX=0000 CX=0000 DX=0000 SP=FFEE BP=0000 SI=0000 DI=0000

DS=1D60 ES=1D60 SS=1D60 CS=1D60 IP=0100 NV UP EI PL NZ NA PO NC

1D60:0100 B80500 MOV AX,0005

-t

AX=0005 BX=0000 CX=0000 DX=0000 SP=FFEE BP=0000 SI=0000 DI=0000

DS=1D60 ES=1D60 SS=1D60 CS=1D60 IP=0103 NV UP EI PL NZ NA PO NC

1D60:0103 BA0900 MOV DX,0009

-t

AX=0005 BX=0000 CX=0000 DX=0009 SP=FFEE BP=0000 SI=0000 DI=0000

DS=1D60 ES=1D60 SS=1D60 CS=1D60 IP=0106 NV UP EI PL NZ NA PO NC

1D60:0106 01D0 ADD AX,DX

-t

AX=000E BX=0000 CX=0000 DX=0009 SP=FFEE BP=0000 SI=0000 DI=000

DS=1D60 ES=1D60 SS=1D60 CS=1D60 IP=0108 NV UP EI PL NZ NA PO NC

Запись в отчёте:

mov ax,5 ; загрузить в регистр АХ число 5

mov dx,9 ; загрузить в регистр DХ число 9

add ax,dx ; сложить содержимое AX и DX, результат=Eh и помещает-

ся в регистр АХ, значения битов флагового регистра

остаются неизменными

1.3.6 Команды U и G отладчика на примере ввода данных с клавиатуры.

Введите A cs:100. Наберите программу:

100 mov ah,3f

102 mov bx,00

105 mov cx,0c

108 mov dx,10f

10b int 21

10d jmp 100

10f db ' '

Нажмите ENTER. Выполните команду U 100,10f. Выполните программу

до шага 10b и введите G 10D, введите данные и проверьте содержимое с адреса

10f. Напишите комментарий к каждой строке.

1.3.7 Определите размер памяти, используя прерывание BIOS int 12h,

для чего необходимо ввести команду "-e cs:100 cd 12 cb <enter>" и выполнить

программу по шагам до команды IRET( в AX-размер памяти).

1.3.8 Определите адрес подпрограммы обслуживания вектора прерыва-

ния n (по указанию преподавателя).

1.3.9 Составьте программу на Ассемблере или на другом языке по ука-

занию преподавателя, получите EXE-модуль и выполните его по шагам с по-

мощью отладчика DEBUG.

22

1.4 Содержание отчета

1.4.1 Название лабораторной работы.

1.4.2 Цель работы.

1.4.3 Рисунки 1.1 и 1.2, а также таблица 1.1.

1.4.4 Результаты выполнения пунктов 1.3.2, 1.3.3, 1.3.4 и 1.3.8 задания к

лабораторной работе.

1.4.4 Фрагменты программ с комментариями пунктов 1.3.5…1.3.7 зада-

ния к лабораторной работе.

1.4.5 Листинг разработанной программы к пункту 1.3.9 задания к лабо-

раторной работе.

1.5 Контрольные вопросы

1.5.1 В чём отличие понятий структуры и архитектуры системы (вычис-

лительной, управляющей, микропроцессорной и т.п.)?

1.5.2 Какие основные компоненты входят в состав микропроцессорной

системы?

1.5.3 Какие элементы микропроцессора являются определяющими при

функционировании процессора?

1.5.4 Какая система счисления является машинным языком? В какой

системе счисления обычно записывают команды на машинном языке? Почему?

1.5.5 Какие архитектурные характеристики микропроцессора представ-

ляют наибольший интерес при его программировании?

1.5.6 Является ли модель МП Intel 8086 моделью фон Неймана и поче-

му?

1.5.7 К какой разновидности архитектур относится архитектура 8086:

RISC, CISC, SIMD, SISD, MIMD?

1.5.8 Перечислите основные группы регистров, входящих в состав МП

8086.

1.5.9 При работе РС в реальном режиме используется сегментный спо-

соб адресации памяти. В чём суть? Поясните на примере с 16-битной шиной

адреса.

1.5.10 Для чего предназначена программа-отладчик DEBUG?

1.5.11 Что такое стек и где он используется? Приведите пример исполь-

зования стека.

1.5.12 Назовите основные признаки отличия RISC - архитектуры МП от

CISC. Что такое конвейерная обработка данных и какой из архитектур МП она

наиболее приемлема: RISC или CISC? Почему?

1.5.13 Какая информация включается в состав слова состояния процес-

сора?

1.5.14 Как организуется в микро-ЭВМ сегментно-страничный способ

управления памятью. Почему этот режим называется защищённым?__

Практическое занятие 14

14. Изучение порядка взаимодействия УУ, АЛУ и ОЗУ при автоматическом выполнении команд

Цель работы

Изучение общих принципов структурной организации ЭВМ и ее ЦП, а также алгоритма выполнения процессором команд

Выполнение работы

1. Запустить обучающее приложение по курсу “Основы ОС” с помощью программы обозревателя.

2. В соответствии с полученным индивидуальным заданием промоделировать выполнение команд.

Моделирование осуществляется по схеме:

o выбор из меню “Команды” изучаемой команды процессора;

o выбор команды “Моделирование”;