Практическая работа №8

Тема: Дешифраторы и шифраторы

Цель: Изучение принципа действия комбинационных схем: дешифратора, шифратора.

Вид работы: индивидуальный

Время выполнения: 2 часа.

Теоретические сведения

Дешифратор (декодер) – это логическая схема с несколькими входами и несколькими выходами, которая преобразует кодированные входные сигналы в кодированные выходные сигналы, причем входные и выходные коды различны. Входной код обычно имеет меньшее число разрядов, чем выходной код, и между входными и выходными кодовыми словами имеется взаимно-однозначное соответствие. При этом каждое входное слово порождает отличное от других выходное кодовое слово.

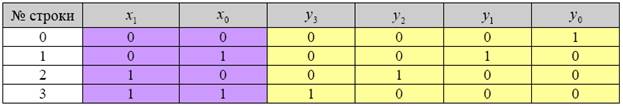

В большинстве случаев роль входного кода играет n-разрядный двоичный код, где n-разрядное двоичное слово представляет одну из 2n различных кодированных величин. Обычно это целые числа от 0 до 2n -1. Иногда для представления меньшего, чем 2n, числа величин, применяют усеченный n-разрядный двоичный код. Например, в двоично-десятичном коде 4-разрядные комбинации от 0000 до 1001 представляют десятичные числа от 0 до 9, а комбинации от 1010 до 1111 не используются. Роль выходного кода играет m-разрядный код «1 из m», у которого в любой момент времени отличен от нуля один бит. Таким образом, в коде «1 из 4» с высоком активным уровнем сигнала на выходах кодовые слова имеют вид: 0001, 0010, 0100 и 1000. А при низком активном уровне сигнала на выходах кодовые слова имеют вид: 1110, 1101, 1011 и 0111. Таблица истинности (ТИ) для дешифратора с двумя входами и с высоким уровнем активного сигнала представлена в таблице 5.

Таблица 5 - ТИ двухразрядного дешифратора

Например, устройство должно иметь 4 выхода. Для каждого выхода записываем логическое выражение на основе СДНФ:

(5)

(5)

где ![]() ,

,

![]() - переменные с отрицанием.

- переменные с отрицанием.

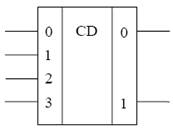

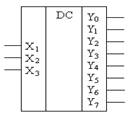

По этой системе выражений строится схема требуемого дешифратора. Условное графическое обозначение такого дешифратора изображено на рис. 9.

Рисунок 9 - Условное графическое обозначение дешифратора

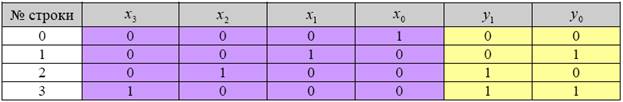

Если код на выходе устройства имеет меньшее число разрядов, чем код на входе, то это устройство обычно называют шифратором (кодером). Шифратор выполняет функцию, обратную декодеру (дешифратору), т.е. преобразует непозиционный (унитарный) двоичный 2n разрядный код в n-разрядный позиционный код. При подаче на один из входов единичного сигнала на выходе формируется соответствующий двоичный код. Таблица истинности для шифратора при n = 2 приведена в таблице 6.

Таблица 6 - ТИ шифратора при n = 2

Система собственных функций для выходов шифратора на основе СДНФ:

![]() , (6)

, (6)

![]() ,

,

где ![]() ,

, ![]() ,

,

![]() ,

, ![]() - переменные с отрицанием.

- переменные с отрицанием.

Условное графическое обозначение такого шифратора изображено на рис. 10.

Рисунок 10 - Условное графическое обозначение шифратора

Ход работы

Дешифратор – это устройство, предназначенное для преобразования двоичного кода в напряжение логической единицы (логического нуля) на том выходе, номер которого совпадает со значением двоичного кода на входе. При n входах в полном дешифраторе имеется 2n выходов, т.е. для каждой комбинации входных сигналов имеется соответствующий выход. Дешифратор, у которого при n входах число выходов меньше 2n, называется неполным. Другое название дешифратора - декодер. Принцип работы полного трехразрядного дешифратора рассмотрим на примере его таблицы истинности.

Входы |

Выходы |

|||||||||

|

X3 |

X2 |

X1 |

Y7 |

Y6 |

Y5 |

Y4 |

Y3 |

Y2 |

Y1 |

Y0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Соответствующие таблице истинности ФАЛ имеют вид

![]() (7)

(7)

![]()

![]()

![]()

![]()

![]()

![]()

![]() .

.

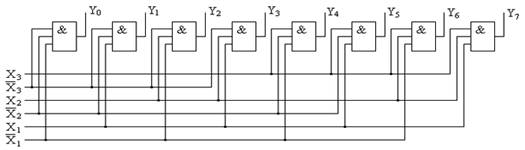

Структурная схема трехразрядного дешифратора, синтезированная на основании полученных ФАЛ приведена на рисунке 11,а, а его УГО - на рис. 11,б.

а)

а)

б)

б)

Рисунок 11 - Структурная схема и УГО трехразрядного дешифратора.

В общем случае логические уравнения для выходных переменных дешифратора n-разрядного числа имеют вид

![]() (8)

(8)

![]()

![]()

![]()

………

![]() .

.

Построенные по полученным формулам дешифраторы называются линейными. К преимуществу линейных дешифраторов можно отнести высокое быстродействие, поскольку входные переменные одновременно поступают на все элементы И. Одновременно, без дополнительных задержек, формируется и результат на выходах этих элементов. Очевидно, что для реализации линейного дешифратора n-разрядного числа необходимо иметь 2n логических элементов И с n-входами. В существующих микросхемах логических элементов количество входов ограничено. Следовательно, ограничена и разрядность реализуемых на их основе линейных дешифраторов, что является недостатком. Кроме того, недостатком является и то, что предыдущие элементы, работающие на входы дешифратора, должны иметь высокую нагрузочную способность, т.е. должны быть рассчитаны на подключение большого числа логических элементов И. Каждый из входов дешифратора подключен к 0,5·2n логическим элементам И. Поскольку нагрузочная способность базовых логических элементов ИС не превышает величины N=10¸20, то максимальная разрядность дешифрируемых чисел для линейных дешифраторов n=4¸5.

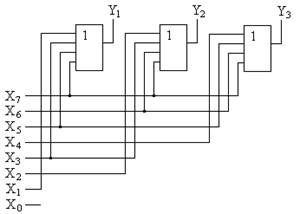

Указанного недостатка лишены пирамидальные дешифраторы. Принцип построения этих дешифраторов состоит в том, что сначала строят линейный дешифратор для двухразрядного числа X1, X2, для чего необходимы 22=4 двухвходовые схемы И. Далее, каждая полученная конъюнкция логически умножается на входную переменную X3 в прямой и инверсной форме. Полученная конъюнкция снова умножается на входную переменную X4 в прямой и инверсной форме и т.д. Наращивая, таким образом, структуру, можно построить пирамидальный дешифратор на произвольное число входов. На рис. 12 приведена структура пирамидального дешифратора для трех разрядов.

Рисунок 12 - Пирамидальный дешифратор для трехразрядного числа.

Характерным отличием пирамидальных дешифраторов от линейных является использование только двухвходовых логических элементов вне зависимости от разрядности дешифрируемого числа. В то же время количество логических элементов в пирамидальном дешифраторе больше. Однако следует иметь ввиду, что количество логических элементов, располагаемых в одном корпусе ИС, определяется главным образом, требуемым количеством выводов. Следовательно, в одном корпусе ИС можно расположить большее число двухвходовых элементов, чем трехвходовых, четырехвходовых и т.д. И значит, пирамидальная структура дешифратора по числу корпусов ИС может оказаться более предпочтительной, чем линейная.

Шифраторы выполняют задачу обратную той, которую выполняют дешифраторы: появление логической единицы (логического нуля) на определенном входе приводит к появлению соответствующей кодовой комбинации на выходе. Также как и дешифраторы, шифраторы бывают полными и неполными. Работа восьмивходового полного шифратора задается следующей таблицей истинности:

|

Входы |

Выходы |

|||||||||

|

X7 |

X6 |

X5 |

X4 |

X3 |

X2 |

X1 |

X0 |

Y3 |

Y2 |

Y1 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

|

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

На основании таблицы истинности можно записать ФАЛ, задающие работу восьмивходового шифратора:

![]() (9)

(9)

![]()

![]() .

.

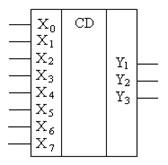

Синтезированная на основании приведенных логических уравнений структурная схема шифратора представлена на рис. 13, а, а его условное графическое обозначение – на рис. 13, б.

а) б)

Рисунок 13 - Структура и УГО восьмивходового шифратора.

Задания к практической работе

Задание 1. Синтезировать дешифратор на 6, 7, 8 или 9 входов. Промоделировать разработанную схему.

Задание 2. Синтезировать двоичный шифратор на 6, 7, 8 или 9 входов. Промоделировать разработанную схему.

Задание 3. Спроектировать линейный дешифратор на 4 входа и шифратор.

Задание 4. Спроектировать пирамидальный дешифратор на 4 входа и шифратор.

Задание 5. Спроектировать матричный дешифратор на 4 входа и шифратор.

Контрольные вопросы и задания

1. Каково назначение и условное графическое обозначение дешифратора?

2. Что называется полным и неполным дешифратором?

3. Приведите схему дешифратора, преобразующий одну декаду двоично-десятичного кода на входе в десятинный код на выходе.

4. Каково назначение шифратора?

5. Дайте определения приоритетного шифратора.

6. Построить приоритетный шифратор на 4 входа в базисе И-НЕ.

7.

Материалы на данной страницы взяты из открытых источников либо размещены пользователем в соответствии с договором-офертой сайта. Вы можете сообщить о нарушении.