Практическая работа №6

Тема: Регистры

Цель: Изучение функциональных свойств универсальных сдвиговых регистров и экспериментальное исследование режимов работы регистра.

Вид работы: индивидуальный

Время выполнения: 2 часа.

Теоретические сведения

Регистры являются наиболее распространенным узлом цифровой техники. Регистр – это внутреннее запоминающее устройство процессора или внешнего устройства, предназначенное для временного хранения обрабатываемой или управляющей информации. Регистры представляют собой совокупность триггеров, количество которых равняется разрядности регистра, и вспомогательных схем, обеспечивающих выполнение некоторых элементарных операций, как установка всех разрядов регистра в «0» и др.

Регистры хранения используются для приема, хранения и выдачи многоразрядного кода. Они представляют собой совокупность одноступенчатых триггеров (как правило, D-или RS-типа) с общим входом синхронизации. Иногда в регистре имеется также и общий вход асинхронной установки всех триггеров в «0».

Регистры сдвига обеспечивают помимо хранения информации, сдвиг влево или вправо всех разрядов одновременно на одинаковое число позиций. При этом выдвигаемые за пределы регистра разряды теряются, а в освобождающиеся разряды заносится информация, поступающая по отдельному внешнему входу регистра сдвига. Обычно эти регистры обеспечивают сдвиг кода на одну позицию влево или вправо. Но существуют и реверсивные регистры сдвига, которые выполняют сдвиг как влево, так и вправо в зависимости от значения сигнала на специальном управляющем входе или при подаче синхросигналов на разные входы регистра. Регистр сдвига может быть спроектирован и таким образом, чтобы выполнять сдвиг одновременно не на одну, а на несколько позиций.

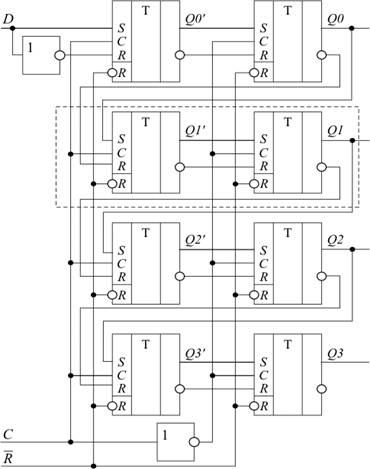

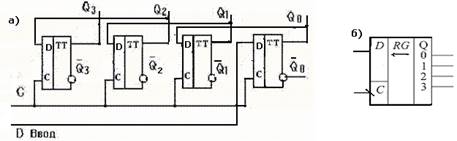

Регистры сдвига строятся на двухступенчатых триггерах. Схема четырехразрядного регистра, выполняющего сдвиг на один разряд от разряда 0 к разряду 3, показана на рис. 17 а его условно-графическое обозначение – на рис. 17. Ввод информации в данный регистр – последовательный через внешний вход D0. Регистр имеет вход асинхронной установки всех разрядов в "0". Для наглядности каждый двухступечатый триггер на схеме представлен двумя одноступенчатыми с соответствующей организацией синхронизации первой и второй ступеней. Пунктиром на схеме выделена часть, образующая двухступенчатый триггер.

Рисунок 17 - Структурная схема регистра сдвига

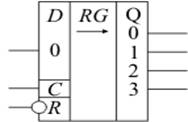

Рисунок 18 - Условно-графическое обозначение четырехразрядного последовательно-параллельного регистра сдвига с асинхронным входом установки в «0»

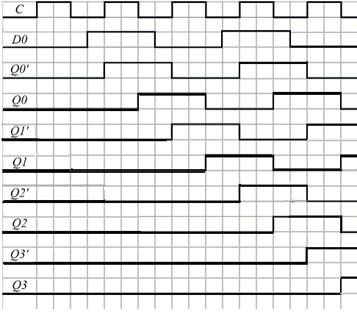

Идеализированная временная диаграмма работы регистра сдвига, структура которого представлена на рис. 17 показана на рис. 19. Предполагаем, что начальное состояние регистра следующее: Q0=0, Q1=0, Q2=0, Q3=0.

Рисунок 19. Временная диаграмма работы регистра сдвига

Работа регистра сдвига в каждом периоде сигнала синхронизации разбивается на две фазы: при высоком и при низком значении синхросигнала:

1. При высоком уровне синхросигнала проводится запись значения выхода (i – 1)-го разряда регистра в первую ступень i-го разряда. Вторая ступень каждого разряда сохраняет свое прежнее значение. В этой фазе состояние первой ступени i-го триггера повторяет состояние второй ступени (i – 1)-го триггера. Вторые ступени каждого триггера, а следовательно, и выходы регистра в целом, остаются неизменными.

2. При низком уровне синхросигнала значение, записанное в первой ступени каждого триггера, перезаписывается в его вторую ступень. Запись в первую ступень триггера запрещена. В этой фазе состояния первой и второй ступеней каждого триггера становятся одинаковыми.

Поступление сигнала R = 0 вне зависимости от значения сигнала на входе синхронизации С и сигнала на входе D0 устанавливает все разряды регистра в нулевое состояние.

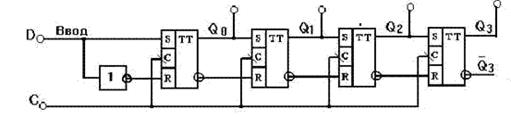

На рис. 20 та же схема того же регистра сдвига на двухступенчатых RS-триггерах, но без асинхронного входа установки в ноль показана, укрупнено, без детализации устройства RS-триггеров. Поскольку данная схема осуществляет сдвиг двоичного слова, установленного на ее выходах вправо, в сторону младших разрядов при каждом спаде синхроимпульса на входе С, то здесь мы имеем дело с динамическим управлением схемой, а синхронизирующие входы, вызывающие переключение соответствующих триггеров в схеме при спаде уровня сигнала на этом входе (т. е. задним фронтом синхроимпульса) называются инверсными динамическими входами. Это обозначено на схеме косой чертой на входе С указывающей на то, что смена состояний (сдвиг) происходит во время перехода высокого уровня синхроимпульса в низкий. Если бы входной сигнал управлял схемой в момент нарастания фронта импульса (передним фронтом импульса) – это было бы прямое динамическое управление, а управляющий вход- прямым динамическим входом и косая черта на схеме указывала бы на переход от низкого уровня сигнала к высокому.

Рисунок 20- Схема регистра сдвига вправо с синхронизацией задним фронтом синхроимпульса

На рис. 21 показана схема регистра сдвига влево, т.е. от младших разрядов к старшим.

Рисунок 21 - Схема регистра сдвига влево с синхронизацией задним фронтом синхроимпульса и его УГО

Сдвиг числа на один разряд влево соответствует умножению сдвигаемого числа на 2. Сдвиг числа на один разряд вправо соответствует делению сдвигаемого числа на 2.

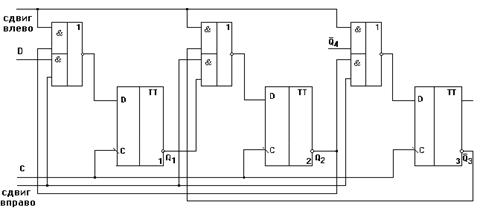

В реверсивном регистре сдвиг данных от разряда к разряду может производиться, как в одну сторону, так и в другую. Схема трехразрядного реверсивного регистра с двумя последовательными информационными входами, для сдвига информации влево и вправо приведена на рис. 22.

Рисунок 22. Схема трехразрядного реверсивного регистра

Регистры сдвига могут выполнять функции и хранения и преобразования информации. Они могут быть использованы для построения умножителей и делителей чисел двоичной системы счисления, т.к. сдвиг двоичного числа влево на один разряд соответствует умножению его на два, а сдвиг вправо - делению на два. Регистры сдвига широко используются для выполнения различных временных преобразований цифровой информации: последовательное накопление последовательной цифровой информации с последующей одновременной выдачей (преобразование последовательной цифровой информации в параллельный код) или одновременный прием (параллельный прием) информации с последующей последовательной выдачей (преобразование параллельного кода в последовательный). Регистры сдвига могут служить также в качестве элементов задержки сигнала, представленного в цифровой форме. Действительно, регистры с последовательным приемом (вводом) и выводом осуществляют задержку передачи информации на m+1 тактов (m+1 - число разрядов регистра) машинного времени.

Как было сказано выше, регистры сдвига синхронизируются фронтом тактирующих импульсов, т.е. запись новой информации в триггеры регистра происходит в течение очень короткого времени - за время длительности фронта синхроимпульса, вернее в момент поступления соответствующего фронта синхроимпульса. Обычно, это «время» значительно меньше времени распространения сигнала, т.е. времени, через которое происходит новое переключение триггера регистра в новое состояние.

Ход работы

Регистром называют последовательностное цифровое устройство, предназначенное для записи, хранения и (или) сдвига информации, представленной в виде многоразрядного двоичного числа. Регистры состоят из простейших ПЦУ – триггеров.

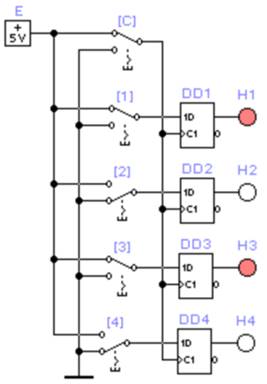

В задании 1 исследуется параллельный регистр (другие названия: регистр памяти, регистр хранения). Данный регистр собран на синхронных D-триггерах. Информационные входы регистра подключены к четырем независимым ключам. Входы синхронизации объединены, что позволяет с помощью ключа С одновременно записать четыре бита во все триггеры регистра.

Процесс параллельной записи можно образно сравнить с процедурой одновременного вручения цветов солдатам, стоящим в одну шеренгу. Цветы солдаты обязаны принимать синхронно (например, по свистку старшины).

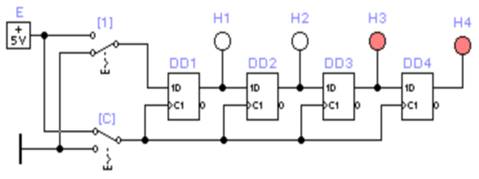

В задании 2 исследуется регистр сдвига (другое название: последовательный регистр).

У этого регистра имеется один информационный вход, с помощью которого вводится информация в регистр. Тактовые входы четырех триггеров объединены, что позволяет синхронно "продвигать" информацию внутри регистра.

В триггер DD1 записывается информация, которая формируется с помощью ключа 1. В триггер DD2 переписывается информация из триггера DD1, в триггер DD3 - из DD2 и т.д.

Если применить метафору, то процесс сдвига информации можно сравнить с передачей по цепочке кирпичей (или арбузов) солдатами, построенными в одну колонну.

Если двоичное число сдвигается от старших разрядов к младшим, то такой процесс называется сдвигом вправо.

В данной практической работе рекомендуется младший бит загружать в триггер А, а старший бит - в триггер D.

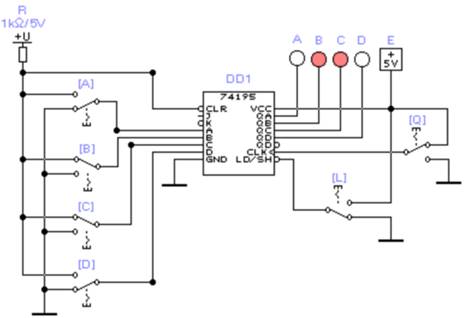

В задании 4 исследуется универсальный регистр 74195.

Чтобы записать в него информацию в параллельном виде нужно операнд подать на входы A, B, C и D. Затем ключ L (LOAD/SHIFT - ЗАГРУЗКА/СДВИГ) поставить в положение «логический ноль», то есть режим «ЗАГРУЗКА». На индикаторах должно появиться загружаемое в регистр число. Дважды нажать ключ Q и тем самым записать подготовленное число в регистр. После этого ключ L установить в положение «логическая единица».

Для сдвига числа на один разряд нужно дважды нажать ключ Q (сдвиг происходит по переднему фронту синхронизирующего импульса).

Задания к практической работе

Задание 1. Исследование параллельного регистра

Собрать схему, показанную на рис. 1.

Поочередно записать в регистр три двоичных числа: все нули, все единицы и двоичное число, которое соответствует последним (младшим) четырем битам первой буквы Вашей фамилии (см. кодовую таблицу CP-1251).

Схему регистра с изображением светящихся индикаторов (для последнего задания) поместить в отчет.

Рисунок 23- Параллельный регистр

Задание 2. Исследование последовательного регистра

Собрать схему, показанную на рис. 23.

Поочередно записать в регистр три двоичных числа: все нули, все единицы и число, которое соответствует последним (младшим) четырем разрядам первой буквы Вашей фамилии (см. кодовую таблицу CP-1251).

Записать в регистр сдвига (рис. 24.) число 3D и умножить его на четыре. Временные диаграммы для последнего задания и схему регистра поместить в отчет.

Рисунок 24 –Последовательный регистр

Задание 3. Исследование универсального регистра

Составить схему, показанную на рис. 25.

Исследовать регистр 74195 в двух режимах: записи и сдвига.

Записать в регистр число 1В (A=1, B=0, C=0, D=0). Сдвинуть это число в сторону старших разрядов на четыре разряда. Зарисовать временные диаграммы.

Записать в регистр число, которое является младшей тетрадой (четыре бита) числа, являющегося представлением второй буквы Вашей фамилии.

Зарисовать временные диаграммы, которые иллюстрируют процесс записи буквы в регистр.

Рисунок 25 - Универсальный регистр

Контрольные вопросы и задания

1. Дайте определение регистра.

2. В чем отличия регистров памяти от регистров сдвига?

3. Объясните причину нецелесообразности применения Т-триггеров для построения регистров памяти.

4. Изобразите схему регистра, позволяющего преобразовывать четырехразрядный параллельный код в последовательный. Объясните работу схемы.

5. Объясните, каким образом в регистре сдвига каждый синхроимпульс обеспечивает сдвиг информации ровно на один разряд.

6. Почему триггеры, синхронизируемые уровнем, не могут быть использованы для построения регистров сдвига?

7. Объясните принцип работы параллельного регистра?

8. Скачано с www.znanio.ru

Материалы на данной страницы взяты из открытых источников либо размещены пользователем в соответствии с договором-офертой сайта. Вы можете сообщить о нарушении.